With electronic and software content in vehicles skyrocketing, and the expectations for flawless operation getting larger, the need for system-level verification continues to grow. Last month, we looked at a Synopsys methodology for virtual hardware in the loop, or vHIL… Read More

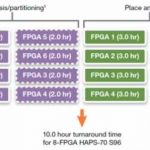

FPGA Prototyping: From Homebrew to Integrated Solutions

Years ago, when FPGA prototyping started, there were no solutions that you could go out and buy and everything was created as a one-off: buy some FPGAs or an FPGA-based board, and put it all together. It was a lot of effort, nobody really knew in advance how long it would take, there was very limited visibility for debug and the whole … Read More

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

Simulating to a fault in automotive and more

We’re putting the finishing touches on Chapter 9 of our upcoming book on ARM processors in mobile, this chapter looking at the evolution of Qualcomm. One of the things that made Qualcomm go was their innovative use of digital simulation. First, simulation proved out the Viterbi decoder (which Viterbi wasn’t convinced had a lot … Read More

Synopsys Q3 Results

Synopsys announced their quarterly results this afternoon. It is the end of their Q3 (yes, they are not on the regular calendar year. Neither, for that matter, is Mentor who announce tomorrow). On the earnings call Aart started off:Good afternoon. I’m happy to report that our third quarter results were very strong, as we achieved… Read More

My Candid Conversation with Karen Bartleson

If you don’t know about Karen Bartleson, before I get into details, let me tell you that she was the President of IEEE-SA for the past 2 years and has been nominated by the IEEE Board of Directors as one of the candidates for IEEE President-Elect for 2016. The IEEE is an organization I admire as it plays a key role in advancing technology… Read More

Design For Safety in Automotive Electronics

Do you remember how auto maker Toyota had to pay a $1.2 billion settlement in 2014 because some of their automotive models experienced sudden, unintended acceleration? That scenario has to be an engineer’s worst nightmare because something was missed during the design and testing of an automotive electronics system that… Read More

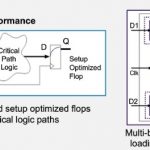

More FPGA-based prototype myths quashed

Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

John Koeter: How To Be #1 in Interface IP

John Koeter is in charge of marketing Synopsys’ IP and prototyping solutions. I talked to him last week.

He grew up in upstate New York, son of a Scottish mother and a Dutch father who immigrated to the US, so he is first generation American, unlike everyone else I’ve interviewed so far for this series who were born overseas.… Read More

Build Low Power IoT Design with Foundation IP at 40nm

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More