I got an invite to the SNUG (Synopsys User Group meeting) keynotes this year. I could only make it to the second keynote but what a treat that was. The speaker was Dr. Peter Stone, professor and chair of CS at UT Austin. He also chaired the inaugural panel for the Stanford 100-year study on AI. This is a guy who knows more about AI than most… Read More

SNUG 2017 Keynote: Aart de Geus on EDA Fusion!

I spoke with Aart before his SNUG keynote and found him to be very relaxed and upbeat about EDA and our future prospects which reminded me of my first ever (cringe-worthy) blog, “EDA is Dead”. Now, eight years later, we have what Aart calls “EDA Fusion” to thank for the reemergence of EDA as a semiconductor superpower, absolutely.… Read More

A Formal Feast

It’s not easy having to deliver one of the last tutorials on the last day of a conference. Synopsys drew that short straw for their tutorial on formal methodologies at DVCon this year. Despite that they delivered an impressive performance, keeping the attention of 60 attendees who said afterwards it was excellent on technical content,… Read More

Virtual Modeling Drives Auto Systems TTM

The electronics market for automotive applications is distinguished by multiple factors. This is a very fast growing market – electronics now account for 40% of a car’s cost, up from 20% just 10 years ago. New technologies are gaining acceptance, for greener and safer operation and for a more satisfying consumer experience. Platforms… Read More

Recipes for Low Power Verification

Synopsys hosted a tutorial on verification for low power design at DVCon this year, including speakers from Samsung, Broadcom, Intel and Synopsys. Verification for low power is a complex and many-faceted topic so this was a very useful update. There is a vast abundance of information in the slides which I can’t hope to summarize… Read More

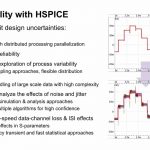

Using HSPICE StatEye to Tackle DDR4 Rail Jitter

The world is a risky place, according to Scott Wedge, Principal R&D Engineer at Synopsys, who presented at the Synopsys HSPICE SIG on Feb 2[SUP]nd[/SUP] in Santa Clara. Indeed, the world circuit designers face can be uncertain. Dealing with risk and departure from ideal was a main theme in the fascinating talks at this dinner… Read More

FPGA Design Gets Real

FPGA’s have become an important part of system design. It’s a far cry from how FPGA’s started out – as glue logic between discrete logic devices in the early days of electronic design. Modern day FPGA’s are practically SOC’s in their own right. Frequently they come with embedded processor cores, sophisticated IO cells, DSP,… Read More

Verifying Design for In-Car Networks

Once upon a time the role of electricity in a car was pretty modest: spark plugs, alternator, lighting, some simple instrumentation and maybe heating, all supported by an equally simple wiring harness (my wife has a 1962 Morris Minor, so I know exactly what the whole wiring harness looks like). How times have changed. Now most or … Read More

SPIE Advanced Lithography and Synopsys!

SPIE is the premier event for lithography held in Silicon Valley and again Scotten Jones and I will be attending. EUV is generally the star of the show and this year will be no different now that TSMC has committed to EUV production in 2019.

Last year at SPIE, TSMC presented the history of EUV development from the beginning in 1985 as … Read More

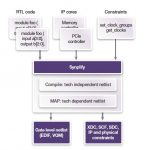

Four Steps for Logic Synthesis in FPGA Designs

I remember meeting Ken McElvain at Silicon Compilers for the first time back in the 1980’s, he was a gifted EDA tool developer that did a lot of coding including logic synthesis, a cycle-based simulator and ATPG. Mentor Graphics acquired Silicon Compilers with Ken included, and he continued to create another logic synthesis… Read More