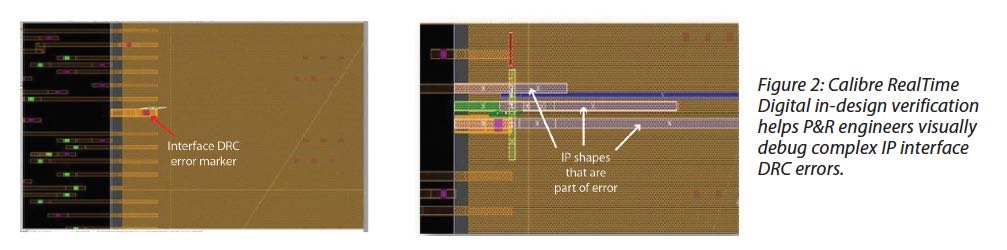

When floor planning (FP) and place & route (P&R) tools took over from custom layout tools for standard cell based designs, life became a lot better for designers of large digital chips. The beauty of the new flows was that all the internals of the standard cells and many IP blocks were hidden from view, lightening the load … Read More

Applying Generative Design to Automotive Electrical Systems

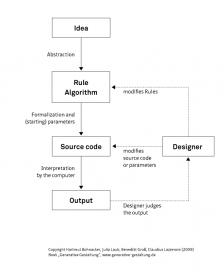

Scanning headlines of technology news every day I was somewhat familiar with the phrase “Generative Design” and even browsed the Wikipedia page to find this informative flow-chart that shows the practice of generative design.

Generative design is an iterative design process that involves a program that will generate… Read More

Specialized AI Processor IP Design with HLS

Intelligence as in the term artificial intelligence (AI) involves learning or training, depending on which perspective it is viewed from –and it has many nuances. As the basis of most deep learning methods, neural network based learning algorithms have gained usage traction, when it was shown that training with deep neural network… Read More

Designing a fully digitally controlled DC-DC buck converter

One of the unsung heroes of our digital world is the modest voltage converter. Batteries and wired power sources rarely match up with the supply needs for advanced ICs. Leading edge ICs have multiple voltage domains and very often, as in the case of processors, use dynamic voltage scaling to help conserve power. Looking at where … Read More

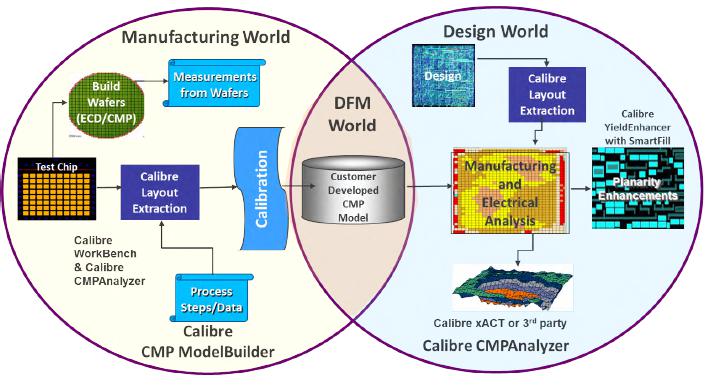

Tackling Manufacturing Errors Early with CMP Simulation

CMP (Chemical Mechanical Planarization or also known as Chemical Mechanical Polishing) is a wafer fabrication step applied generally after a chemical deposition –intended to smoothen and to flatten (planarize) wafer surfaces with the combination of chemical and mechanical forces. Developed at IBM and since its introduction… Read More

Emulation Evaluation for the Ages!

One of the more entertaining things I get to observe in the semiconductor ecosystem is competitive customer evaluations of tools and IP. Seriously, this is where the rubber meets the road no matter what the press releases say.

This time it was emulators which is one of the most interesting EDA market segments since there is no dominant… Read More

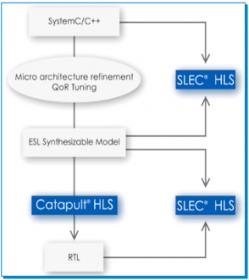

Sequential Equivalency Checks in HLS

Higher level synthesis (HLS) of an IP block involves taking its high-level design specification –usually captured in SystemC or C++, synthesizes and generates its RTL equivalent. HLS provides a faster convergence path to design code stability, promotes design reuse and lowers front-end design inception cost.

HLS and Mentor… Read More

Improving Library Characterization with Machine Learning!

For SOC designers that are waiting for library models the saying “give me liberty or give me death” is especially apropos. Without libraries to support the timing flow, SOC design progress can grind to a halt. As is often the case, more than just a few PVT corners are needed. Years ago, corners were what the term sounded like – the 4 corners… Read More

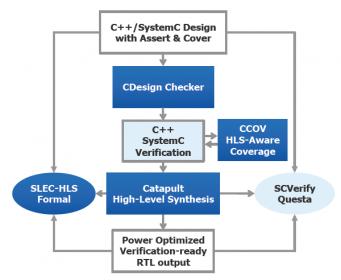

Catapult Design Checker Finds Coding Errors Before High Level Synthesis

In a recent whitepaper Gagandeep Singh, Director of Engineering at Mentor, a Siemens Business outlines a flow using Catapult Design Checker that helps in early detection of coding errors as many companies are turning to High-Level Synthesis (HLS) methodology. This requires that high -level C++ models are correct, that ambiguities… Read More

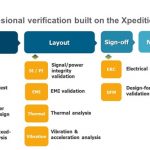

Eliminate PCB Re Spins using an Integrated Multi Dimensional Verification Platform

The rapidly increasing complexity of today’s designs, combined with schedule pressure to deliver innovative products to market as quickly as possible, strains engineering resources to the limit, often to the point of breaking. As a result, 17% of all projects get canceled, and another 28% miss their target release date (Source:… Read More