When floor planning (FP) and place & route (P&R) tools took over from custom layout tools for standard cell based designs, life became a lot better for designers of large digital chips. The beauty of the new flows was that all the internals of the standard cells and many IP blocks were hidden from view, lightening the load on the tools and designers. So-called footprints, in the form of Library Exchange Format (LEF) files, filled in for the internals of these cells and blocks.

A properly constructed LEF cell view is frequently adequate to give the P&R tool the ability to produce design rule correct final GDS level layout. But not always. Final DRC is always needed. As design sizes increased and the loop from final whole chip DRC to fixes and verification became unwieldy and not practical for highly sensitive chip design schedules.

This is the issue that Qualcomm encountered in their flow while designing extremely large state of the art SOCs. I recently had the chance to read a white paper that talks about the issues that Qualcomm encountered and how they solved them with Mentor’s Calibre RealTime Digital in-design DRC. Let’s look at the primary issues that they encountered.

LEF files contain an abstract of the underlying layout called a footprint. However, as the cells and blocks are placed in a design there are a large number of interactions that can take place between these cells that could lead to DRC violations. Waiting until late in the design cycle to verify all the base layer design rule correctness can leave serious issues baked into the design until they are much more difficult to fix.

The other source of issues are interactions between routing in the P&R tool and the geometry inside of the placed cells. A cause of this issue can be errors in the LEF cell views. In this case the errors might not be caught until the entire design is exported and merged with the contents of the placed cells. For large designs like those in development at Qualcomm, the chip level operation to merge all the geometry in the design can take a long time.

The white paper describes the process that Qualcomm adopted using Mentor’s Calibre RealTime Design solution. Instead of doing a merge of the entire design and running batch DRC, Calibre RealTime Digital makes direct calls to the Calibre engine running foundry qualified sign-off Calibre rule decks. It is able to run analysis on the area in proximity to where designers are working. It enables incremental DRC while in the P&R tool, including all the layout layers and nested cells and blocks that are normally not available from the P&R tool. As a result, designers get nearly instantaneous feedback on violations and feedback on potential fixes.

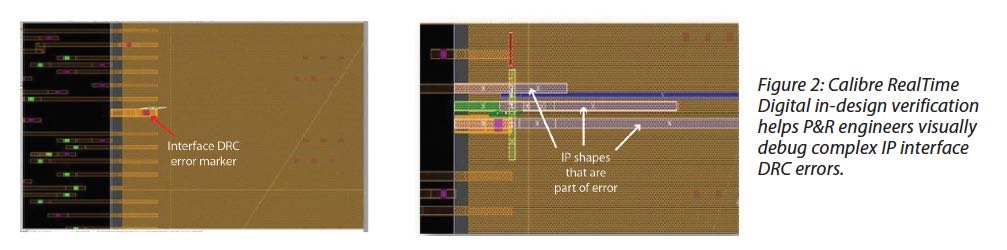

When geometry in inside placed cells is part of violation, selected shapes contained in the cells or blocks is shown to help designers fully understand the error, so a fix can quickly be made. This is really the best of both worlds, designers can still work efficiently in the P&R tool environment, yet they are able to detect and understand problems that arise due to the fully merged geometry and all layers.

It was years ago that Calibre completely disrupted the DRC market with the introduction of its easy to use and highly effective hierarchical capabilities. Customers immediately understood the competitive advantage that they would gain by using Calibre. The Calibre RealTime Digital interface looks to be another game changing capability to come from this formidable development team. Based on the white paper it seems that Qualcomm agrees with this sentiment.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.