Despite NoCs being finely tuned in legacy subsystems, when subsystems are connected in larger designs or even across multi-die structures, differing traffic policies and system-level delays between NoCs can introduce new opportunities for deadlocks, livelocks and other hazards. Paul Cunningham (GM, Verification at Cadence),… Read More

Electronic Design Automation

A Closer Look at Conquering Clock Jitter with Infinisim

As voltages go down and frequencies increase, the challenges in chip design become increasingly complex and unforgiving. Issues that once seemed manageable now escalate, while new obstacles emerge, demanding our attention. Among these challenges, clock jitter stands out as a formidable threat. At its core, clock jitter is… Read More

Podcast EP243: What is Yield Management and Why it is Important for Success with Kevin Robinson

Dan is joined by Kevin Robinson, yieldHUB’s Vice President of Operations who was recently appointed Head of Sales for Europe, the Middle East & Africa. With over 23 years of experience as a test engineer in the semiconductor industry, Kevin brings a wealth of knowledge and dedication to his dual role. At yieldHUB, Kevin leads… Read More

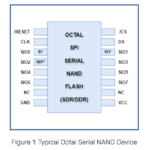

Overcoming Verification Challenges of SPI NAND Flash Octal DDR

As the automotive industry continues to evolve, the demands for high-capacity, high-speed storage solutions are intensifying. Autonomous vehicles and V2X (Vehicle-to-Everything) communication systems generate and process massive amounts of data, necessitating advanced storage technologies capable of meeting these… Read More

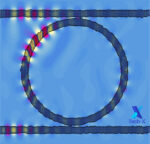

Introducing XSim: Achieving high-quality Photonic IC tape-outs

Similar to analog circuits, which use EM waves at communications frequencies, components in photonics integrated circuits (PICs), which use EM waves at optical frequencies, are sensitive to layout and manufacturing variations—arguably more so. Similar to their semiconductor counterparts, which transmit information… Read More

Synopsys IP Processor Summit 2024

Now that live events are filling up there are even more live events especially here in Silicon Valley. Synopsys, the #1 full IP provider, will host a processor summit here in Santa Clara next month. Given the popularity of anything RISC-V, I would expect this event to be very well attended so be sure and register in advance.

The networking… Read More

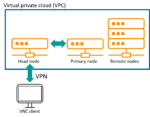

What are Cloud Flight Plans? Cost-effective use of cloud resources for leading-edge semiconductor design

Embracing cloud computing is highly attractive for users of electronic design automation (EDA) tools and flows because of the productivity gains and time to market advantages that it can offer. For Siemens EDA customers engaged in designing large, cutting-edge chips at advanced nanometer scales, running Calibre® design stage… Read More

The Impact of UCIe on Chiplet Design: Lowering Barriers and Driving Innovation

The semiconductor industry is experiencing a significant transformation with the advent of chiplet design, a modular approach that breaks down complex chips into smaller, functional blocks called chiplets. A chiplet-based design approach offers numerous advantages, such as improved performance, reduced development … Read More

First third-party ISO/SAE 21434-certified IP product for automotive cybersecurity

Increased processing and connectivity in automobiles are cranking up the priority for advanced cybersecurity steps to keep roads safe. Electronic vehicle interfaces, including 5G/6G, Bluetooth, Wi-Fi, GPS, USB, CAN, and others, offer convenience features for drivers and passengers, but open numerous attack vectors for… Read More

Circuit Simulation Update from Empyrean at #61DAC

A familiar face in EDA, Greg Lebsack met with me in the Empyrean booth at DAC this year on opening day to provide an update on what’s new. I first met Greg when he was at Tanner EDA, then Mentor and Siemens EDA, so he really knows our industry quite well. The company was a Silver level sponsor of DAC this year, and Empyrean offers tools for… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior