You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

The Cadence-BDA saga continues with Berkeley Design Automation today filing a motion to dismiss. You can read the full motion HERE. My previous blog “Cadence Sues Berkeley Design Automation” with 30+ comments is HERE.

The first problem BDA brings up is that the DMCA claim by Cadence is so vague that it doesn’t… Read More

Last night at Cadence was the next installment of what I have been calling Hogan University. Jim interviewed Joe Costello about how to tell a story as part of the EDAC emerging companies series of events. The main focus was how to tell a story as a small EDA company communicating with investors, although there are obviously other forms… Read More

DAC has several “Insight Presentations” on Wednesday June 5th. Bryan Bowyer from Calypto will be presenting from 2-4pm that day (don’t know where, the DAC website doesn’t have a room number specified yet). The topic is Reducing Design and Debug Time with Synthesizable TLM. TLM, of course, stands for… Read More

DAC is in Austin this year, as I’m sure you know, and DAC has keynotes by CEOs of two Austin-based companies Freescale Semiconductor and National Instrument. Two more keynotes (one split into two) are focused on mobile, which has become the major driver of semiconductor today. A fifth keynote, including presentation of … Read More

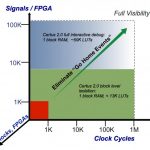

ASIC prototyping in FPGAs is starting to trend on SemiWiki. As FPGA technology becomes more advanced customers tell me that the traditional debug tools are inadequate. Faced with the very restrictive debugging capabilities and very long synthesis/place/route times the debugging cycle in these prototype platforms are quite… Read More

Very often we talk about increasing design complexities and verification challenges of SoCs. With ever growing design sizes and multiple IPs on a single SoC, it’s a fact that SoC design has become heterogeneous, being developed by multiple teams, either in-house or outsourced. Considering economic advantage amid pressure … Read More

IC designers involved with physical design are familiar with acronyms like DRC (Design Rule Check), LVS (Layout Versus Schematic) and DFM (Design For Manufacturing), but how would you go about checking for compliance with ESD (Electro Static Discharge) rules? You may be able to kludge something together with your DRC tool and… Read More

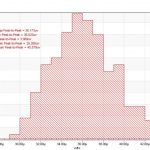

Mobile applications require CMOS image sensor devices that have a low signal-to-noise ratio (SNR), low power, small area, high resolution, high dynamic range, and high frame rate. CMOS image sensor imaging performance is noise limited requiring accurate noise analysis on the pixel array electronics and column readout circuitry.… Read More

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More

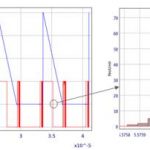

Tanner EDA Applications Engineers see a broad range of technical challenges that our users are trying to overcome. Here’s one worth sharing – it deals with transient noise analysis (TNA) for a comparator design. The customer is a producer of advanced flow measurement devices for application in medicine and research. The designer… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era