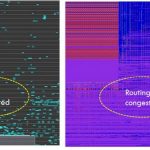

As an applications engineer for over 15 years supporting physical design tools that enable implementation closure, I have seen the complexity of timing closure grow continuously from one process node to the next. At 28nm, the number of scenarios for timing sign-off has increased to the extent that is way beyond the number that … Read More

Electronic Design Automation

Design IP round #2: after road-test, time for the race

Design IP, at least Interface IP, is about 15 years old, but the market was made of one large provider – Synopsys- with many small vendors around. Chip makers were not very comfortable with this picture, especially the Tier 1 considering that the risk (to see the big one being acquired by one of their direct competitor, say Samsung… Read More

Improving Design Practices for an Image Sensor IDM

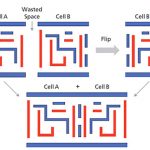

With nearly twenty five years in business, Tanner EDA Application Engineers have seen a wide range of support requests. One consistent topic area is around design data management and design reuse. In one recent instance, our customer, an IDM who produces imaging sensors for infrared vision systems, called on Tanners AE team for… Read More

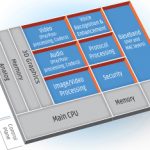

How To Design a TSMC 20nm Chip with Cadence Tools

Every process node these days has a new “gotcha” that designers need to be aware of. In some ways this has always been the case but the changes used to be gradual. But now each process node has something discontinuously different. At 20nm the big change is double patterning. At 14/16nm it is FinFET.

Rahul Deokar and John… Read More

Bangers: the Best Beer Bar in Austin; Live Oak Brewing, the Best Beer in Austin

OK, enough with all this semiconductor geeky stuff. The important thing about DAC is…where to go to eat to avoid standard issue convention center chicken Caesar salad.

And a 7 minute walk from the convention center is Bangers Sausage House and Beer Gardenwhere you can have the $8 “executive” lunch consisting… Read More

Wireless Algorithm Validation from System to RTL to Test

This year’s #50DAC will be chock-full of technical content because that is what attracts the masses of semiconductor professionals, like moths to a flame, or like me to a Fry’s Electronics store. Interesting note, I went to high school with Randy Fry. His Dad started the Fry’s supermarket chain which he sold… Read More

A Brief History of Dassault Systèmes

Dassault Systèmes (DS) was created in 1981 when a small team of engineers were spun out of Dassault Aviation. They were developing software to design wind-tunnel models and so reduce the cycle time for wind-tunnel testing, using surface modeling in 3D instead. The company entered into a distribution agreement with IBM that same… Read More

Global Foundries Does DAC

Global Foundries will be at DAC in booth 1314. There will be 6 pods there demonstrating:

- Advanced Technology: 28nm ready and ramping, and next is 20LPM and 14XM.

- PDKs: For 28nm, 20nm and 14nm. 14nm handles FinFET enablement complexity. Robust, easy to use and high quality, supports pretty much the full range of EDA tools.

- Design

Cell-Aware Test Seminar

You may have heard about cell-aware testing. It’s a transistor-level test (ATPG) methodology that is quickly becoming a hot topic. If you are involved in DFT and are looking for better quality and reliability, you should definitely know about cell-aware testing.

And lucky you, on May 16, 2013, you can attend a free seminar on cell-aware… Read More

Sage Design Automation iDRM Launch

This is an example of what I do during the day. I work with emerging companies on disruptive technologies and help launch them into the fabless semiconductor ecosystem. This product, iDRM, is the result of three years of joint development work amongst three semiconductor foundries and some of their top customers:… Read More

CEO Interview with Aftkhar Aslam of yieldWerx