You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

This year’s version of Bill Deegan’s DAC App for iPhone is now available for download from the iTunes App Store. The App has the entire calendar included, and makes it easy to add any interesting looking event to your calendar. The whole exhibit hall can be searched and there is a zoomable map of the exhibit hall.

I have… Read More

Two weeks ago I blogged about analog verification and it started a discussion with 16 comments, so l’ve found that our readers have an interest in this topic. For decades now the Digital IC design community has used and benefited from regression testing as a way to measure both design quality and progress, ensuring that first… Read More

I talked with a mystery person earlier this week. I would love to tell you his (or her) name and the company he (or she) works for but they are the sort of company that doesn’t casually endorse any suppliers so it all has to remain anonymous. But they have been a customer of Pinpoint, originally from Tuscany Design Automation until… Read More

Honestly speaking, there is no firm answer to this question, and often when we get confronted by our customers, we talk about the coverage reports. The truth is a product with high rate of coverage can very easily fail in customer environment. Of course coverage is important, and to be clear about the fact that the failure is not because… Read More

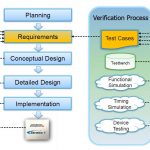

Word association: if I said “requirements management”, you’d probably say IBM Rational “DOORS,” or maybe Serena or Polarion if you come from the IT world. But what if the requirements you need to manage are for an FPGA or ASIC, with HDL and testbench code and waveform files and more details backing verification, and compliance… Read More

Bats about DAC!by SStalnaker on 05-23-2013 at 8:05 pmCategories: EDA, Siemens EDA

DAC 2013 is closing in fast now…and if you haven’t made your plans for what you want to see and do, you’d better get going! Of course, I’m happy to help you out with a few suggestions…starting with that most important objective—conference swag. Stop by the Mentor Graphics booth (#2046, for those of you who actually look at your floor… Read More

As we get down to smaller and smaller process nodes, the problem of soft errors becomes increasingly important. These soft errors are caused by neutrons from cosmic rays, alpha particles from materials used in manufacture and other sources. For chips that go into systems with high reliability this is not something that can be ignored.… Read More

One of the most useful ways to learn about an EDA tool is to talk with other users that have experience with that tool. IC Place and Route tools are complex and yet necessary to implement every SoC designed today, so at DAC in just two weeks you have a chance to hear first-hand from several P&R tool users. To get a better idea about these… Read More

Nvidia designs some of the most powerful graphics chips and systems in the world, so I’m always eager to learn more about their IC design methodology. This week I’ve had the chance to talk with Ting Ku, Director of Engineering at Nvidia about his DAC talkin the Apache booth in exactly two weeks from today. Registration… Read More

As I have mentioned before, Cliosoft is the biggest little company in EDA with the most talked about products on SemiWiki. At DAC, ClioSoft will introduce integrated SOS design management (DM) solutions providing revision control, design management and multi-site team collaboration for Aglient Technologies’ Advanced Design… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry