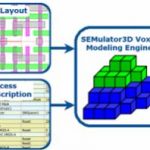

Yes, it’s a pleasant surprise; it is Virtual Fabrication Platform, one of the new innovations in 2013. I was looking around for what kind of breakthrough technologies will be announced in DAC this year. And here I came across this new kind of innovative tool which can produce final virtual fabricated 3D structures after following… Read More

Electronic Design Automation

DAC lunch seminar: Better IP Test with IEEE P1687

What: DAC lunch seminar (register here)

When: June 5, 2013, 11:30am – 1:30pm

Where: At DAC in lovely Austin, TX

Dr. Martin Keim of Mentor Graphics will present this overview of the new the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG.

If you are involved in IC test*, you’ve probably heard about IJTAG. If you … Read More

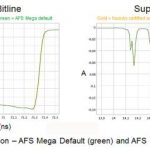

TSMC ♥ Berkeley Design Automation

As I mentioned in BDA Takes on FinFET Based Memories with AFS Mega:

Is AFS Mega real? Of course it is, I’m an SRAM guy and I worked with BDA on this product so I know. But don’t take my word for it, stay tuned for endorsements from the top SRAM suppliers around the world.

Here is the first customer endorsement from the #1 foundry.… Read More

Atrenta: Mentor/Spyglass Power Signoff…and a Book

Today Atrenta and Mentor announced that they were collaborating to enable accurate, signoff quality power estimation at the RTL for entire SoCs. The idea is to facilitate RTL power estimation for designs of over 50M gates running actual software loads over hundreds of millions of cycles, resulting in simulation datasets in the… Read More

Advanced Verification – HW/SW Emulation – SoC/ASIC Prototyping

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

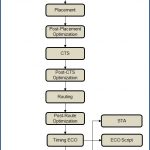

Efficient Handling of Timing ECOs

Today, in the design of any type of system on chip (SoC), timing closure is a major problem and it only gets worse with each new, and more advanced process technology. Timing closure is closely inter-leaved with power and clock design. The complexity of achieving closure rises sharply with increasing design density and advancing… Read More

The Hot Zone: Do Good While Having Fun

The big 50th Anniversary party for DAC is on Monday night at the home of Austin City Limits. However, you can do good while enjoying yourself and also get into “The Hot Zone”, an exclusive area within the party in the penthouse Jack and Jim Gallery. The Gallery features 30 original photographs from the godfather of music… Read More

BDA Takes on FinFET-based Memories with AFS Mega

Berkeley Design Automation today announced the first silicon-accurate circuit simulation for mega-scale arrays like memories and CMOS image sensors. If this tool lives up to its claims, it is going to be a big deal for FinFET-based circuits, Memory designers are rightly worried about having the accuracy necessary to include… Read More

RTL Signoff Theater

We have talked for years about RTL signoff, the idea that a design could be finalized at the RTL level and then most of the signoff would take place there. Then the design would be passed to a physical implementation team who would not expect to run into any problems (such as routing congestion, missing the power budget or similar problems).… Read More

Transistor, Gate and RTL Debug Update at DAC

Debugging an IC design at the transistor, Gate and RTL levels is often necessary to meet timing requirements and understand analog or digital behavior, yet the process itself can be a tedious one, filled with manual steps, therefore making it an error-prone process. EDA tools have been created to help us graphically debug transistor,… Read More

Quantum Computing Technologies and Challenges