We have already discussed the recently released M-PCIe ECN from PCI-SIG in Semiwiki at the end of 2012, but the new “standard” (in fact an Engineering Change from PCI-SIG and MIPI Alliance) was only real on paper, at that time. The upcoming webinar from Synopsys, M-PCIe: Utilizing Low-Power PCI Express in Mobile Designs, shows … Read More

Electronic Design Automation

LSI’s Experience With Formality Ultra

LSI is an early adopter of Formality Ultra, Synopsys’s tool for improving the entire ECO flow. I already wrote about the basic capability of the tool here. ECOs are changes that come very late in the design cycle, after place and route has already been “nearly” completed. They occur either due to last minute spec… Read More

Something old, something new in SystemC HLS

Perhaps no area in EDA has been as enigmatic as high-level synthesis (HLS). At nearly every industry event, some new-fangled tool always seems to be tabbed as the next big thing by some analyst or pundit. In a twist, the latest news is on one of the oldest tools – CybeWorkBench.… Read More

Ten Ways Your Synchronizer MTBF May Be Wrong

Estimating the MTBF of an SoC should always include an analysis of synchronizer reliability. Contemporary process nodes are introducing new challenges to the reliability of clock domain crossings so it is prudent to revisit how your simulation tool calculates a synchronizer’s MTBF. Let’s list the ten most common pitfalls.… Read More

The TSMC OIP Technical Paper Abstracts are up!

The TSMC Open Innovation Platform® (OIP) Ecosystem Forum brings TSMC’s design ecosystem member companies together to share with our customers real-case solutions for customers’ design challenges and success stories of best practice in TSMC’s design ecosystem.

More than 90% of the attendees last year said “this… Read More

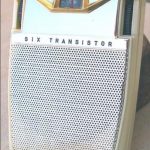

Low-Power Design Analysis and Optimization for Mobile and High-Performance Computing Applications

For several decades now consumers like me have enjoyed using mobile devices including:

- Transistor radios, my first one had just 6 discreet transistors in the 1960’s

- HP 21 Calculator, used in college with Reverse Polish Notation, circa 1976

- Zenith Data Systems laptop, with two floppy drives, 1980’s

- Palm Pilot V,

20nm IC production needs more than a ready Foundry

I think by now all of us know, or have heard about 20nm process node, its PPA (Power, Performance, Area) advantages and challenges (complexity of high design size and density, heterogeneity, variability, stress, lithography complexities, LDEs and so on). I’m not going to get into the details of these challenges, but will ponder… Read More

Jasper: Negronis on tap

Did you know that Jasper’s Corner Tap in San Francisco serves Negronis on tap? It’s true. They also have Hanky Panky on tap, which is a Negroni with the Campari replaced with Fernet (which everyone pronounces as Frenet despite it being…well…wrong). And here’s another thing you probably didn’t… Read More

Innovation + Thoughtful Management = Productive Expansion

After looking at various aspects of this company, to sum up, I couldn’t find any better statement than this; thoughtful management here is actually leadership with passion which achieves tangible results. This reflects in the methodology of doing things in this company which has given it a place among top EDA companies in a span… Read More

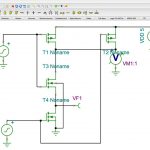

Web-based Circuit Design and Analysis

Last month I blogged about CircuitLaband received some two dozen comments, so clearly there is keen interest in using web-based tools for electronic circuit design and using the cloud to save designs plus run simulations. Today I’m reporting on TINACloud, provided by a company called DesignSoft. … Read More

Solving the EDA tool fragmentation crisis