Cliff Hou of TSMC gave the keynote today at SNUG on Collaborate to Innovate: a Foundry’s Perspective. Starting around 45nm the way that a foundry has to work with its ecosystem fundamentally changed. Up until then, each process generation was similar enough to the previous one, apart obviously from size, that it could be … Read More

Electronic Design Automation

Will 14nm Yield?

If I had a nickel for every time I heard the term “FinFET” at the 2013 SNUG (Synopsys User Group) Conference I could buy a dozen Venti Carmel Frappuccinos at Starbucks (my daughter’s favorite treat). In the keynote, Aart de Geus said FinFET 14 times and posed the question: Will FinFETs Yield at 14nm? So that was my mission, ask everybody… Read More

In compliance we trust, for integration we verify

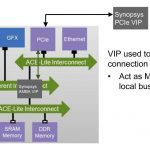

So, you dropped that piece of complex IP you just licensed into an SoC design, and now it is time to fire up the simulator. How do you verify that it actually works in your design? If you didn’t get verification IP (VIP) with the functional IP, it might be a really long day.

Compliance checking something like a PCIe interface block is a … Read More

Moore Push Versus Market Pull

I was at SNUG earlier today at both Aart’s keynote that opened the conference and at his “meet the press” Q&A just before lunch. The keynote was entitled Bridges to the Gigascale Decade. And the presentation certainly contained lots of photos of bridges! Anyway, I’m going to focus on just one thing,… Read More

New ways for High Frequency Analysis of IC Layouts

Amidst frequently changing requirements, time pressure and demand for high accuracy, it is imperative that EDA and design companies look at time consuming processes in the overall design flow and find alternatives without losing accuracy. High Frequency Analysis of IC designs is one such process which is traditionally based… Read More

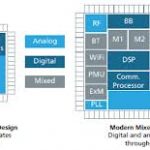

A New Mixed-Signal IC Router

Pure digital routers for IC designs have an easier task than mixed-signal routers, because mixed-signal routers have more constraints like:

- Shielded buses

- Differential pairs

- Twisted pairs

- Matched RC routing

- 20nm technology rules

- Double Patterning Technology (DPT)

Unlocking the Full Potential of Soft IP

EDA vendors, IP suppliers and Foundries provide an eco-system for SoC designers to use in getting their new electronic products to market quicker and at a lower cost. An example of this eco-system are three companies (TSMC, Atrenta, Sonics) that teamed up to produce a webinar earlier in March called: Unlocking the Full Potential… Read More

Mixed-Signal SoC verification has integrated solution

These days when we talk of SoC verification, what comes to our mind immediately is VirtualPlatform. Of course with the increasing size, complexity and different styles of designs, it is very much a need.

However, that is supported by actual verification engines and methodologies which are varying considerable with digital, … Read More

A Brief History of Forte Design Systems

When Semiwiki readers see the name Forte Design Systems, they may think of the live bagpipers’ performance that closes the yearly Design Automation Conference. Forte has been the sponsor of this moving end to DAC since 2001. Step with me behind the plaid kilts for a good look at this remarkable company headquartered in San Jose, … Read More

Data Management for Designers

Back when I was a programmer at VLSI Technology in the mid-1980s, I was responsible for all the data management in the VLSI Design Tools. By responsible for, I mean that I designed the whole system and wrote all the code. Prior to the 5th release of our product, there was no data management, designers simply used filenames and it was … Read More

Facing the Quantum Nature of EUV Lithography