You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4389

[filter] => raw

[cat_ID] => 157

[category_count] => 4389

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

DAC is coming up in a month (OMG less than 4 weeks and we are so not ready I hear a hundred marketing people cry out). That gives you four weeks (and a couple of days) to tell Mentor what you do in your spare time that you are passionate about (spare time, I hear a hundred engineers cry out, what is that?) and you could win $300.

For DAC, Mentor… Read More

I will say that as popular as DO-254 and the like is, I am not the fella for that. It can take the simplest of designs into a realm of test and verification like you have never seen before. Yes, when I am flying I happen to be a big fan of this rigorous testing but you will not find me doing that job anytime soon. While the topic is very dry, it … Read More

DACis just 33 days away and who wouldn’t want a cool GoPro camerato play with? Your manager will certainly want you to first check out what’s new at DAC if your job involves getting to RTL signoff on time and within budget. The creative folks at Atrenta have figured out how to attract us with the offer of winning a GoPro camera,… Read More

ANSYS acquired Apache Design Automation back in June 2011and three years later the name “Apache” is being subdued in favor of using just ANSYS. One thing that I noticed right away was a DACfocus on having actual ANSYS customers talk about their hands-on experience using the EDA tools. The following seven customers… Read More

The big three in EDA are well-know for offering AMS and RF IC design flows, but today you also have alternative EDA vendors available that have capable tools, yet are lessor known. This blog will present an overview of the AMS and RF IC design flowoffered by Silvaco, an EDA company with a strong history in TCAD tools like Utmost IV for… Read More

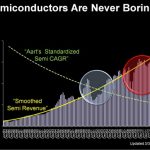

Every industry has famous thought leaders that can summarize where we’ve been and then paint a picture of where we’re headed towards in the future. Often they make statements that become industry expressions, like “Moore’s Law” or the “Internet of Things”. I think that if Synopsys… Read More

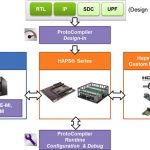

I recently published a post on LinkedIn titled “Sometimes, you gotta throw it all out” in reference to the innovation process and getting beyond good to better. A prime example has crossed my desk: the new ProtoCompiler software for Synopsys HAPS FPGA-based prototyping systems.

Last week, I spoke with Troy Scott, product marketing… Read More

Tanner EDA is making waves at their customer’s sites as the mixed-signal design suite from Tanner EDA, Incentia Design Systems, Inc. and Aldec, Inc. helps ASIC Design House lower cost and increase efficiency with no compromise in performance. In today’s ‘always on’, Internet of Things connected world, the demand for high-performance,… Read More

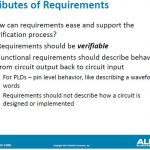

Last week I had the pleasure of presenting at the Electronic Design Process Symposium (EDPS) workshop. This was my first time attending and I was very impressed. There were good presentations but I learned as much from the Q&A and the side conversations before/after/breakfast/lunch/etc. If you have the opportunity to attend,… Read More

I think by now a lot has been said about the necessity of multi-patterning at advanced technology nodes with extremely low feature size such as 20nm, because lithography using 193nm wavelength of light makes printing and manufacturing of semiconductor design very difficult. The multi-patterning is a novel semiconductor manufacturing… Read More

Is Intel About to Take Flight?