Digital semiconductor design flows predominantly use library models (typically verilog and liberty formats) for static analyses. Design sizes continue to grow and geometry continues to shrink. Demand for superior performance continue to increase. Accuracy of the library models has become more critical than ever before … Read More

Electronic Design Automation

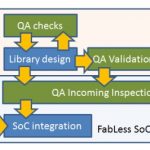

How About a Quality-Aware IP Design Flow

In the EDA world we use hyphens quite often to describe our technical approaches, like: DFM-aware, Power-aware, Variation-aware. I just read a white papertoday on the topic of Quality-Aware IP Design Flows, written by Fractal Technologies. If your group creates IP or re-uses IP, then there’s always the question about … Read More

RedHawk Excels – Customers Endorse

Since a few years, I have been following up Ansys Apachetools for semiconductor design, verification and sign-off. RedHawk is the most prominent platform of tools from Ansys, specifically for Power, Noise and Reliability Sign-off. It has witnessed many open endorsements from several of Ansyscustomers through open presentations,… Read More

Understanding QoR in FPGA synthesis

We’ve all heard this claim: “Our FPGA synthesis tool produces better quality of results (QoR).” If you’re just hoping for a tool to do that automagically, you’re probably doing it wrong. Getting better QoR depends on understanding what an FPGA synthesis tool is capable of, and how to leverage what it tells you.… Read More

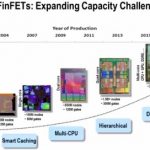

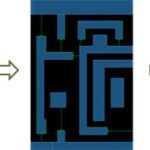

DRM2PDK: From design rule manual to process design kit

Exactly a year ago Sage Design Automation launched its revolutionary iDRM product, enabling for the first time to graphically capture design rules and compile them into checks automatically – no programming required. Using the graphical design rule editor, users could draw the layout topology that describes the design… Read More

Two New ESL Tools for Power and Thermal at DAC

Gary Smith published a list of what to see at DAC, and I noticed that he listed DOCEA Power in a category of ESL Thermal. I’ll be meeting the DOCEA engineers on Wednesday at DAC to learn more about their two newest ESL products:

- Thermal Profiler

- Power Intelligence

In general DOCEA Power tools allow you to manage power and thermal… Read More

Different Approaches to System Level Power Modeling and Analysis for Early Design Phases

At DATEthis year in Dresden, Bernhard Fischer from Siemens CT(Corporate Technology) has presented an interesting summary of the various techniques used for power modeling and analysis at the architectural level. He went through the pros and cons of using spreadsheets, timed virtual platforms annotated with power numbers … Read More

Mark Milligan Joins Calypto. Plus Google at DAC

I talked to Mark Milligan this morning, who has just joined Calypto as VP Marketing. I first met Mark back when he was at CoWare and I was at VaST or maybe it was Virtutech. Then he moved on and ran marketing at SpringSoft which, I’m sure you remember, Synopsys acquired. I asked him what encouraged him to join Calypto.

He said that… Read More

Methodics @ #51DAC!

This is the biggest year ever for Methodics at DAC, with lots to show, and a team of people excited to talk to customers and potential customers alike. Methodics will also be giving away Pebble Smartwatches!

Methodics theme for DAC2014 is “IP and design management done right”. A key part of this message is to show how their unique open… Read More

Cadence Go (war-game) strategy

I was attending to CDN-Live in Munich last week, so I was expecting Cadence to announce new IP related acquisition like Lip-Bu Tan did last year (Cosmic Circuit, Evatronix and Tensilica). In fact, Lip-Bu was not in Munich and Charlie Huang, SVP Worldwide Field Operations and System & Verification Group, was holding the morning… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry