DRVerify is part of the iDRM design rule compiler platform from Sage DA, something that I have been personally involved with for the past three years. DRVerify is mainly used to verify third party design rule check (DRC) decks and ensure that they correctly, completely and accurately represent the design rule specification. In… Read More

Electronic Design Automation

Verification of Power Delivery Networks

Power delivery networks (PDN) are the metal structures on a chip that delivers the power. In a high-end desktop SoC this might be delivering as much as 150W, and with voltages around 1V that means over 150 amps of current. Clearly getting the PDN correct is critical for a correctly functioning chip. One of the challenges to verifying… Read More

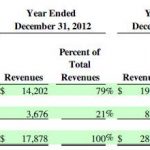

HDMI, DisplayPort, MHL IPs + Engineering Team = Good Move

This news is certainly not as amazing that the acquisition of MIPS by Imagination, or Arteris by Qualcomm… but it shows that Cadence is building a complete Interface IP port-folio, brick after brick. The result will be that a complete wall is being built on the Synopsys road to monopoly and complete success on Interface IP market.… Read More

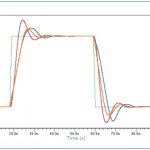

Speeding Up AMS Verification by Modeling with Real Numbers

My first introduction to modeling an AMS behavior using a language was back in the 1980’s at Silicon Compilers using the Lsim simulator. Around the same time the VHDL and Verilog languages emerged to handle the modeling of both digital and some analog behaviors. The big reason to model analog behavior with a language is for… Read More

I switched to Aldec Active-HDL

I have written this before, but I was a ModelSim snob. That has changed after trying Active-HDL from Aldec. I have no plans on going back to ModelSim. You ask why? Well astute reader, great question. Unfortunately these blogs are text limited and there is no way to write about all the bells and whistles of Active-HDL. So before I continue,… Read More

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More

Designing an SoC with 16nm FinFET

IC designers contemplating the transition to 16nm FinFET technology for their next SoC need to be informed about design flow and IP changes, so TSMC teamed up with Cadence Design Systems today to present a webinar on that topic. I attended the webinar and will summarize my findings.

Shown below is a 3D layout concept of an ideal FinFET… Read More

Update on AMS Verification at DVcon

Digital verification of SoCs is a well-understood topic and there’s a complete methodology to support it, along with many EDA vendor tools. On the AMS (Analog Mixed-Signal) side of the design world life is not so easy, mostly because there are no clear standards to follow.

To gain some clarity into AMS verification I spoke… Read More

TI – The Initial Innovator of Semiconductor ICs

[TI’s China Foundry acquired from SMIC]

During my engineering graduation, electronic design courses and mini-projects, the ICs I used to come across were SN 7400 series from Texas Instrumentsthat covered a large range of devices from basic gates and flip-flops to counters, registers, memories, ALUs, system controllers, and… Read More

Has LinkedIn Jumped the Shark?

LinkedIn is without a doubt the number one social network for semiconductor professionals. Based on my experience, the big LinkedIn boom came with the massive unemployment during the Great Recession of 2009. In my estimate, unemployment was 12%+ at the high point in Silicon Valley and resumes clogged the internet with LinkedIn… Read More

Should Intel be Split in Half?