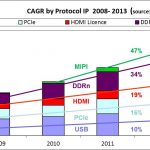

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

Electronic Design Automation

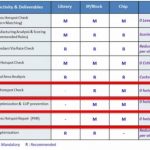

Using Cadence PVS for Signoff at TowerJazz

TowerJazzis a specialty foundry that provides IC manufacturing into several markets, like: RF, high-performance analog, power, imaging, consumer, automotive, medical, industrial and aerospace/defense. In June there was a presentation from Ofer Tamir of TowerJazz at DACin the Cadence theatre, so I had a chance this week … Read More

How Sonics Uses Jasper Formal Verification

The Jasper part of Cadence announced jointly with Sonics a relationship whereby Sonics uses JasperGold Apps as part of their verification. I talked to Drew Wingard, the CTO, about how they use it.

One way is during the day when their design engineers use Jasper as part of their verification arsenal. Interestingly it is the design… Read More

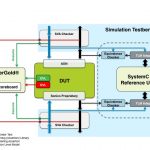

Power-Aware Verification in Mixed-Signal Simulation

My Samsung Galaxy Note 2 phone lasts about 1.5 days on a single battery charge, thanks in part to the clever power conservation approaches like when the screen is automatically dimmed then turned off after no activity. Mobile phones and many other battery-powered devices used today all need power-saving designs, which then means… Read More

Look who is Leading the World Semiconductor Business

A couple of days ago I was reading a news article which said how long the world economy will be dependent on a single engine to drive it; obviously that single engine is USA. If we consider the overall economy, definitely USA is driving it, and semiconductor is a large part of it. The semiconductor is driving electronics and that is attracting… Read More

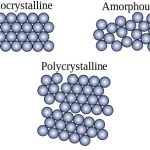

Amorphous Silicon and TFTs

Most ICs are fabricated with crystalline silicon (c-Si), which is a tetrahedral structure forming a well-ordered crystal lattice. There’s another form of semiconductor material called amorphous silicon (a-Si) which has no long-range periodic order. It turns out that a-Si is a great material for the active layer in thin-film… Read More

Lucio and the Kaufman Award

Tuesday was the Kaufman award dinner. This year it was awarded to Lucio Lanza. Last week I wrote about how Lucio ended up in EDA, although that was not where he finished up. He is currently a venture capitalist running Lanza Technology Ventures, one of the few VCs to make any investments in the EDA/IP/semiconductor space. Also, unlike… Read More

Semiconductor Safety

Semiconductors and automotive are now like peanut butter and jelly. Certainly you can have one without the other but why would you? I remember when a car first talked to me telling me that the door was ajar. It sounded more like, “the door is a jar” but I got the point. Now my car tells me just about everything including what is wrong with… Read More

In-Design DFM Signoff for 14nm FinFET Designs

While FinFET yield controversy is going on, I see a lot being done to improve that yield by various means. One prime trend today, it must be, it’s worthwhile, is to pull up various signoffs as early as possible during the design cycle. And DFM signoff is a must with respect to yield of fabrication. This reminds me about my patents filed… Read More

Its a bouncing baby IEEE standard!

Pass the cigars! On November 3rd, 2014, the IEEE-SA Standards Board finally approved IEEE P1687 as a new standard. From now on, you can drop the “P” and just call it 1687, or to its friends, IJTAG. Now would be a good time to sign up for an IJTAG technical workshop.

The new IEEE 1687 Internal JTAG (IJTAG) standard is changing… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era