When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

Electronic Design Automation

Place & Route with FinFETs and Double Patterning

Place & route in the 16/14nm era requires a new approach since it is significantly more complex. Of course, every process generation is more complex than the one before and the designs are bigger. But modern processes have new problems. The two biggest changes are FinFETs and double patterning.

FinFETs, as I assume you know,… Read More

A Complete Timing Constraints Solution – Creation to Signoff

With the unprecedented increase in semiconductor design size and complexity design teams are required to accommodate multiple design constraints such as multiple power domains for low power design, multiple modes of operation, many clocks running, and third party IPs with different SDCs. As a result timing closure has become… Read More

SiC and Si Power Devices

ICs for consumer electronics are often battery powered, which are considered low voltage designs. On the other end of the IC spectrum are high voltage devices used in many industrial applications like: automotive, aerospace, data centers, transportation and power generation. … Read More

Mentor at TSMC OIP, 16nm, and 10nm

On Tuesday, September 30, TSMC hosts another Open Innovation Platform Ecosystem forum at the San Jose Convention Center. Have you registered? This year includes 30 technical sessions from TSMC’s ecosystem partners, divided into three separate tracks. I’ll be hanging out in the EDA track, listening to various takes on 16nm FinFET… Read More

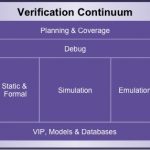

Synopsys Verification Continuum

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required… Read More

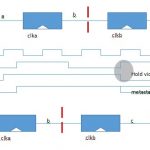

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

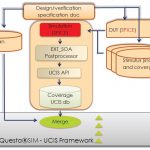

Coverage Driven Verification for Analog?

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

Electro-Thermal Simulation of Power Transistors

Power transistors are commonly used in applications like: hybrid vehicles, electric vehicles, automotive, home appliances, LED lighting, TVs, power and energy. In the old days an engineering team could build their device with power transistors, then after production run some thermal testing to see if they guessed the proper… Read More

Explaining HAPS-DX in an elevator

Every development team has been through this challenge: finding a tool that looks fantastic, then heading off to the manager one or two levels up who has enough signature authority for the purchase order. Signatures for amounts reading more than a couple of trailing zeros on POs are rarely free, or painless. … Read More

Weebit Nano Moves into the Mainstream with Customer Adoption