When I studied mathematical analysis, one of the things that we had to prove turns out to be surprisingly difficult. If you have a continuous function and at one point it is below a line (say zero) and at another point it is above zero, then there must be a point at which the value is exactly zero. In effect, a continuous function can’t… Read More

Electronic Design Automation

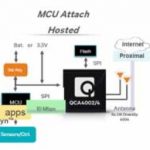

Xtensa core in Qualcomm low-power Wi-Fi

Wi-Fi has this reputation as being a power hog. It takes a relatively big processor to run at full throughput. It is always transmitting all over the place, and it isn’t very efficient at doing it. Most of those preconceived notions arose from older chips targeting the primary use case for Wi-Fi in enterprise and residential environments.… Read More

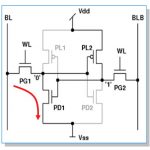

Optimizing SRAM IP for Yield and Reliability

My IC design career started out with DRAM at Intel, and included SRAM embedded in GPUs, so I recall some common questions that face memory IP designers even today, like:

- Does reading a bit flip the stored data?

- Can I write both 0 and 1 into every cell?

- Will read access times be met?

- While lowering the supply voltage does the cell data retain?

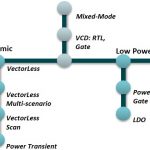

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

Simulating to a fault in automotive and more

We’re putting the finishing touches on Chapter 9 of our upcoming book on ARM processors in mobile, this chapter looking at the evolution of Qualcomm. One of the things that made Qualcomm go was their innovative use of digital simulation. First, simulation proved out the Viterbi decoder (which Viterbi wasn’t convinced had a lot … Read More

4 Design Tips for AVB in Car Infotainment

Audio Video Bridging (AVB) is a well-established standard for in-car infotainment, and there is a significant amount of activity for specifying and developing AVB solutions in vehicles. The primary use case for AVB is interconnecting all devices in a vehicle’s infotainment system. That includes the head unit, rear-seat entertainment… Read More

Why You Really Need Chip-Package Co-analysis

There’s only one software company that I know of that covers four major disciplines: Fluids, Structures, Electronics and Systems. That company is ANSYS and when they acquired Apache Design Automation back in 2011 they filled out their products for electronics design, and more specifically in the area of integrated chip-package… Read More

Moore’s law observations and the analysis for year 2019.

As semiconductor professionals we all are familiar with Moore’s law. Respected Gordon Moore during year 1965-1975 observed and stated that, number of transistors in dense Integrated Circuit has doubled for approximately two years. In the present scenario, if we consider the complexity of Integrated Circuit and if we… Read More

GaN Technology — Contributing to Medicine in No Small Way

In past posts, the disruptive nature of gallium nitride (#GaN) semiconductor technology, especially eGaN® FETs, was discussed…now with significantly higher performance at an equivalent cost, the inevitability of GaN displacing the aging power MOSFET is becoming clearer.

This post highlights a specific end-use application… Read More

A Security Idea for EDA / Embedded Design

I’m on a mission to find novel ideas for EDA / embedded design tools. One I have been discussing on and off with a DARPA friend for at least a couple of years is how to grade the security of a hardware design or, more comprehensively, the security of an embedded system including hardware and the software running on the hardware.

This feels… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center