The quarterly numbers are out from the EDAC Market Statistics Service (MSS) for Q2. The headline number is that revenue for the industry increased by 8.5% for Q2 to $1906.5M versus $1759.9M in Q2 last year. The four quarter moving average, that smooths out a lot of seasonality by comparing the most recent four quarters to the prior… Read More

Electronic Design Automation

Automotive MCU code fault-busting with vHIL

With electronic and software content in vehicles skyrocketing, and the expectations for flawless operation getting larger, the need for system-level verification continues to grow. Last month, we looked at a Synopsys methodology for virtual hardware in the loop, or vHIL… Read More

IoT need Low-cost, Low-power…and Silicon Proven IP

Today, IoT devices are available in our daily life through wearable, smart appliances or metering application and some prediction call for 33 billion connected objects, 25 billion being IoT by 2020 (Gartner, 2014). Being very synthetic, IoT device (smart appliance or wearable object) will be wirelessly and securely connected… Read More

Indian Railways and SoCs

Last week I woke up late as usual and decided to flip through the news paper on Coffee to enjoy the lazy Sunday morning, but I ended up reading a sad news about a train accident. Everyday virtually we hear about minimum one accident. Indian Railways, wow, what a reliable transportation system we have built. It clearly indicates we have… Read More

Prototyping the Future of Semiconductors!

With major semiconductor mergers and acquisitions running rampant in 2015 (more than double the M&A activity in 2014), the question is where will we go from here? There are many different ways to slice this but for this blog let’s talk about the thousands of semiconductor professionals that will be changing jobs as a result … Read More

Nine Cost Considerations to Keep IP Relevant

It’s about 15 years the concept of IP development and its usage took place. In the recent past the semiconductor industry witnessed start of a large number of IP companies across the globe. However, according to Gary Smith’s presentation before the start of 52[SUP]nd[/SUP] DAC, IP business is expected to remain stagnant for next… Read More

Together At Last—Combining Netlist and Layout Data for Power-Aware Verification

The market demanded that gadgets it loves become ever more conscious of their power consumption, and chip designers responded with an array of clever techniques to cut IC power use. Unsurprisingly, these new techniques added to the complexity of IC verification. When you’re verifying a design that has 100+ separate power domains,… Read More

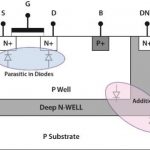

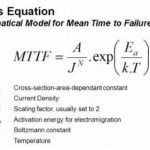

Electromigration Analysis and FinFET Self-Heating

FinFET processes provide power, performance, and area benefits over planar technologies. Yet, a vexing problem aggravated by FinFET’s is the greater local device current density, which translates to an increased concern for signal and power rail metal electromigration reliability failures. There is a critical secondary… Read More

Why Sidense OTP is Like the Armored Car of NVM

I have written about Sidense before, but last week at the TSMC Open Innovation Platform Forum, I had a chance to hear a talk by, and have lunch with Betina Hold Director of R&D at Sidense. Here is what I learned.

Sidense has been focusing on the growing market in what they like to call the smart connected universe. It is best to think… Read More

Enterprise Design Management Comes of Age

The motivations for having a data and process management system in place for semiconductor design have existed for a long time. I am reluctant to admit it, but I remember early efforts to do this back in the 80’s at Valid Logic. Cadence was also developing this capability in house through the early 90’s. Back then designs were much … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center