Qualcomm buckles up for 4G machine communications and the technologies it has picked hint on the most likely winners in the crowded space of the Internet of Things (IoT) standards for machine-to-machine (M2M) communications.… Read More

Electronic Design Automation

Will the Snapdragon 820 Overheat?

So, I happened to read an article today about overheating issues on the snapdragon 820 from rather flaky sources. To guess the answer to this question, one has to understand the snapdragon 810 “heat-gate” and the sequence of events that led to it.… Read More

How to Live with Rapid Changes During Early Development of IP

Best practices call for using a version control system with systematic releases when developing IP. However, in the early stages of IP development using a rigid version control system with a cumbersome release process can hinder productivity. To fully understand how this works we should start by defining what is meant when we … Read More

How Can Big Data and EDA Tools Help?

Big data is a headline phrase that I see appear almost weekly now in my newsfeed, so it’s probably time that I start paying more attention to the growing trend because it does impact how technology-driven, EDA tool flows are being used. From my last trip to DAC I recall only two companies that were really focused on system-level… Read More

Is This a Dagger Which I See Before Me?

Macbeth may have been uncertain of what he saw but, until recently, image recognition systems would have fared even less well. The energy and innovation put into increasingly complex algorithms always seemed to fall short of what any animal (including us humans) is able to do without effort. Machine vision algorithms have especially… Read More

Shifting Low Power Verification to an IP to SoC Flow

One of the most exciting recent developments in low power design and verification is the successive refinement flow developed by ARM® and Mentor Graphics®.… Read More

SpyGlass World 2015 User Group Meeting

I attended SpyGlass World this week – to give you an update, to catch up with old friends, including users, and to meet some of the new (to me) players from the Synopsys side of the event. The event was held in the United Club at Levi stadium, just like last year. Don’t know if this will continue. Merging the SpyGlass User Group into SNUG… Read More

Free Copy of EDAgraffiti!

Last month we offered a free PDF version of our book “Fabless: The Transformation of the Semiconductor Industry”, for the greater good. More than thirteen thousand people have downloaded it thus far so we would like to keep the momentum going with another book giveaway. Paul McLellan has graciously offered his book… Read More

Why Your IP Release Methodology Can Make or Break Reuse Success

When the term IP first came into popular usage for IC design, it was primarily conceived as blocks of design content that were bought occasionally from external sources. A customer might use one or two in a design, and expect one delivery with perhaps some minor updates before tapeout. Over the last 18 years, this notion has changed… Read More

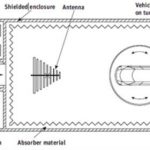

Simulating Full-System EMI for a Car in Just 28 Minutes

While there’s a lot of cool technology in modern semiconductors, it’s important to raise our sights periodically to understand how well these chips will work in the systems for which they are designed. One area driving a lot of semiconductor growth is automobile electronics. We’ve had drive-train control forever it seems, but… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center