You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4440

[filter] => raw

[cat_ID] => 157

[category_count] => 4440

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

At TSMC’s OIP Symposium last month, Zhe (Jared) Lui of HiSilicon presented their experiences with Synopsys’ ICC2 physical design suite.

Jared started by giving an overview of Huawei and HiSilicon. HiSilicon is the semiconductor arm of Huawei. I assume everyone knows who Huawei is. To a first approximation they … Read More

Verification with Tcl for what? – part 2by Anatoly Myshkin on 11-10-2015 at 7:00 amCategories: EDA

In Orion Bytes we use Tcl both for the internal research, product and different verification services. We use also SystemVerilog UVM and Python based Cocotb for different approaches. I think it’s no need to deep into the SystemVerilog and UVM principles here – today’s main verification fashion is well described through… Read More

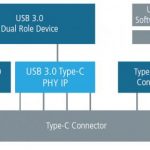

At the early days of Semiwiki (March 2011), I wrote about ThunderBolt, predicting low market adoption of the protocol, for various reasons. One of these reasons was the cost associated with ThunderBolt integration by the OEM. Even if the protocol (associating PCI Express and DisplayPort) was offering better data bandwidth than… Read More

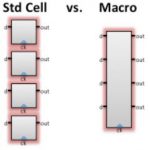

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More

When I first moved to Oregon in 1978 the largest industry was forestry, but then the endangered Spotted Owl was found and that put an end to many forestry companies and decimated the economy of many rural cities. Strangely enough it turns out that the Spotted Owl was found in great numbers across multiple states, so it never should’ve… Read More

Success stories are great. Reading how someone uses a product contributes much more insight than reading about a product. Last month we had a teaser for a presentation by Wave Semiconductor; this month, we have the slides showing how they are using FPGA-based prototyping, AXI transactions, and DPI to speed up development.

First,… Read More

Michael Sanie (Senior Director Marketing in the Synopsys Verification Group) gave the wrap-up presentation at SpyGlass World recently, on the Synopsys Verification Direction. I learned from an interview Michael gave to Paul McLellan that he is an accomplished pianist. I’m a pianist also, though of considerably less talent,… Read More

Often when a company starts out it takes a while for it to find the sweet spot in the marketplace. Very often it is feedback from existing customers and business success that can help point the way for small companies as they grow. This is just as true in EDA as it is in retailing or consumer products. For instance, Mentor Graphics, though… Read More

Verification with Tcl for what?by Anatoly Myshkin on 11-02-2015 at 7:00 amCategories: EDA

Nowadays, verification as one of the most complex SoC, FPGA, and ASIC development flow stages always requires new approaches. The following is an introduction to TcL vs/ with SystemVerilog and VHDL, the first in a 3 part series. Part 2 will be “Tcl vs Python, Bluespec” and part 3 will be “VerTcl description”.… Read More

In 1492 Christopher Columbus sailed from Spain towards west on Atlantic Ocean in search of Asia and Indies. Between his four voyages (1492 – 1502) he discovered many different islands and then what we call Americas. Although he had a compass with him, imagine searching a needle in a haystack. Even with localization of areas and then… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center