To fans of Godel, Escher and Bach (the Eternal Golden Braid), there is an appealing self-referential elegance to the idea of verifying a network switch in a cloud-like resource somewhere on the corporate network. That elegance quickly evaporates however when you consider the practical realities of verifying such device in ICE… Read More

Electronic Design Automation

HLS with ARM and FPGA Technologies Boosts SoC Performance

The way SoC size and complexity are increasing; new ways of development and verification are also evolving with innovative automated tools and environment for SoC development and optimization. IP based SoC development methodology has proved to be the most efficient for large SoCs. This needs collaboration among multiple players… Read More

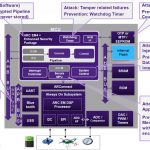

How to Secure IoT Edge Device from Multiple Attacks?

In the 1990’s, designing for performance was the main challenge and the marketing message for Intel processors was limited to the core frequency. Then designers had to optimize power consumption to target mobile phones/smartphone and build power efficient SoC, low power but high performance devices. Now in 2015 the semi industry… Read More

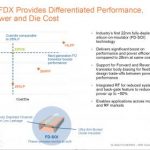

Globalfoundries 22FDX Technology Shows Advantages in PPA over 28nm Node

I really enjoy ARM Techcon when it rolls around every year because it has such a wide range of topics and exhibits. You can find maker gadgets, IoT information, small boards for industrial control, software development kits, semiconductor IP vendors as well as the big EDA players and foundries. This year after perusing the exhibit… Read More

Breaking the Limits of SoC Prototyping

Earlier this month during my conversation with Dr. Walden C. Rhines, he emphasised the need for our next generation designers to think at system level and design everything keeping the system’s view in mind. The verification will go through major transformation at the system level. I can see the FPGA prototyping systems already… Read More

The EDAC Wally Rhines Roast (video)

Last week was the EDAC Phil Kaufman award dinner. It was much more like a roast, probably because Wally has a great sense of humor and as Aart de Geus said, “Wally is a cool cat to have a beer with…” Aart is right of course, hanging with Wally is one of my favorite work things to do.

The place was lousy with media people so I will try and add some… Read More

Maybe Clockless Chip Design’s Time has Come

There have always been novel technologies vying to compete with conventional design practices. It is hit or miss on the success of these ideas. In the 90’s I recall speaking to someone who was convinced that they could effectively build computers based on multilevel logic. This, as we know did not pan out. But there have been many … Read More

A (R)evolution in Hardware-based Simulation Acceleration

The most exciting products in our industry are those that are both evolutionary and revolutionary. Cadence has just announced an update to their hardware simulation acceleration platform – Palladium Z1 – which continues the evolution of the unique capabilities of processor-based acceleration, plus a revolutionary approach… Read More

A Novel Microprocessor Fighting Dark Silicon, Energy Efficiency, Code density and Silicon area

Processor cores used in computers and smartphones have become impaired by their own complexity and can’t fully utilize future CMOS generations for increasing their efficiency. Due to the continued increase of density and speed of transistors, these big cores produce too much heat per mm[SUP]2[/SUP] if trying to follow Moore’s… Read More

Merger Mania: The Future of the Semiconductor Industry

In a semiconductor industry which appears maturing, we are also seeing the technologies unravelling newer transistor structures, memories, processors, and newer ways of designing ICs and electronic systems. The present decade appears to be at the cusp of a new transformation in the semiconductor industry. Amid a slew of mergers… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center