It often seems that semiconductor industry coverage focuses on large digital markets like microprocessors or high frequency analog designs for RF applications. Yes, these are large markets, but power transistors like IBGT and VFETS make up a large and crucial sector. Not only do they make their way into discretes, but they are… Read More

Electronic Design Automation

Academia and TCAD Grow Closer

On my first trip to Austria for EDA business I traveled by car from Germany, and I couldn’t wait to see how fast we would travel on the fabled Autobahn. Oddly enough it was summertime and the Autobahn was filled with vacationing families driving cars with shiny, aluminum campers in tow, so our car only traveled about 60 mph, nothing… Read More

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

5 ways FPGA-based prototyping shrinks design time

Engineers are trained to think linearly, along the lines of we started here, then we did this, and that, and this other stuff, and here is where we ended up. If you’ve ever presented in an internal review meeting, sales conference, or a TED-like event, you know that is a dangerous strategy in winning friends and influencing people.… Read More

An Easier Way to Reach Design Closure for SoC

It’s really challenging to reach design closure of an SoC by meeting timing constraints, staying within the power budget, tracking progress, communicating within the team, minimizing the floorplan, maximizing manufacturability and eliminating hotspots. Most SoC design teams have EDA tools from multiple vendors,… Read More

2016 EDA Dead Pool

The most commonly asked question during conference calls with Wall Street of late is in regards to the massive consolidation the semiconductor industry is experiencing. How will the consolidation affect the Foundries? How will the consolidation affect EDA and IP? How will the consolidation affect the semiconductor industry… Read More

Coming to a Workstation Near You: Accellera’s Portable Stimulus Standard

Portable Stimulus has become such a popular standards topic of late that I thought it would be good to take a break this month from my low power series to bring you, my valued readers, more information about it from one of my colleagues, Dennis Brophy, who is working to help drive development of this standard within Accellera. I’ll … Read More

How to Gain Low-Power at High-Performance

In a world of smart devices, high performance is required in order to address several specific needs such as intelligent and immediate data processing for IoT applications, instant response from mobile devices, highly interactive user interfaces, and so on. Most of these devices are battery operated and hence require lower … Read More

Mentor takes IoT devices to cloud and back

Walking into the Mentor Graphics booth at ARM TechCon, I was greeted by my friends Warren Kurisu and Shay Benchorin. It was good to see them both again. They were poised in front of a table with a Samsung tablet and a small Wi-Fi-ish box, next to a large Samsung printer. The demonstration was similar to a lobby check-in process, where… Read More

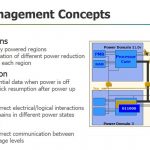

Power Reduction Verification Techniques Highlighted by Mentor at ARM Techcon

Power management is a perennial topic these days, and it came up in several presentations at the recent ARM Techcon in Santa Clara in mid November. The techniques covered in these talks address dynamic and static power consumption. The IEEE 1801 standard deals with specifying power design intent in Universal Power Format (UPF)… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center