Customer perspectives on a tool are always interesting, as much for why they felt the need for the tool as how it is working out for them in practice. Active-Semi, an emerging leader in power management and digital motor drive ICs gave a presentation at CDNLive describing why they adopted ClioSoft tools for design collaboration … Read More

Electronic Design Automation

ARM and Mentor talk about Real Time Virtualization, Webinar

Processor cores come in a wide variety of speeds, performance and capabilities, so it may take you some time to find the proper processor for your system. Let’s say that you are designing a product for the industrial, automotive, military or medical markets that has an inherent requirement for safety, security and reliability… Read More

Mentor’s Battle of the Photonic Bulge

A few weeks back I wrote an article mentioning that Mentor Graphics has been quietly working on solutions for photonic integrated circuits (PICs) for some time now, while one of their competitors has recently established a photonics beachhead. One of the most common challenges for PIC designs is their curvilinear nature, thus… Read More

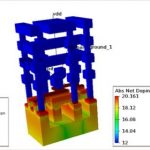

It’s Better than SUPREM for 3D TCAD

Process and device engineers have a tough task to model and simulate an IC process prior to fabricating silicon, however this approach is much better than the alternative choice in the 1970’s of just running multiple lots of wafers and then making measurements to see if your node was meeting specifications. Out of Stanford… Read More

The Future of FPGA Prototyping!

This interview originally appeared as the foreword to our book “Prototypical: The Emergence of FPGA-based Prototyping for SoC Design” but I thought it would be worth publishing for those of you who have not downloaded it yet. I also wanted to mention that our friends at S2C are currently offering a 50% discount on the… Read More

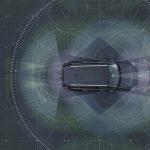

Nvidia Drives into New Market with Deep Learning and the Drive PX 2

Nvidia has found that video games are the perfect metaphor for autonomous driving. To understand why this is so relevant you have to realize that the way self-driving cars see the world is through a virtual world created in real time inside the processors used for autonomous driving – very much like a video game. It’s a little bit like… Read More

These 2 Markets to Drive IC Market Growth through 2020

Spotting trends is an essential insight for marketing folks, general managers and C-level executives in our semiconductor industry. You could read hundreds of press releases, attend dozens of conferences, and interview all of the major thought leaders to help spot an emerging trend, or you could subscribe to a service like IC… Read More

Expert Interview: Rajeev Madhavan

This blog was originally posted on Paysa.com but since Rajeev Madhavan is one of our EDA Heroes I thought it was worth a re-post. In case you do not know Rajeev, he started his EDA career at Cadence then was co-founder and VP of Engineering at LogicVision (acquired by Mentor). Next he was Founder, President, and Chairman of Ambit Design… Read More

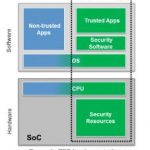

How to Secure a SoC while Keeping Area and Power Competitive?

I have attended LETI conference last June and remember the paper presented by Alain Merle, their security guru. Alain said that smart cards are secured because up to 50% of the Silicon area is dedicated to security. When you design a SoC to address applications like smart metering, NFC payment or embedded SIM, you know in advance … Read More

CEO Interview: Rene Donkers of Fractal Technologies

Fractal is another one of those very successful emerging EDA companies that you don’t read a lot about, except on SemiWiki. Rene Donkers is co-founder and CEO of Fractal Technologies, a company addressing IP quality assurance. This is a niche in the SoC tooling market that deserves some justification. Why not use an IP as-is… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center