The difficulty of managing the power domains on a complex SoC led to the development of a power format file description, to serve as the repository for data needed for functional and electrical analysis (e.g., CPF, UPF). Yet, what about complex printed circuit boards? How can the power domain information be effectively represented… Read More

Electronic Design Automation

Searching for Extraterrestrials

Since the beginning of time, people on Earth have peered into the night sky, pondering if they were alone in the universe. Today, we have a large group of scientists that are working to answer that question. The precision required for their search often depends on the performance of a key piece of technology – the analog-to-digital… Read More

New Protocol (NB- IoT) Requires New DSP IP and New Business Model

If we agree on the definition of IoT as a distributed set of services based on sensing, sharing and controlling through new nodes, we realize that these nodes are a big hardware opportunity. The chip makers and IP vendors have to create innovative SoC, delivering high performance at low cost and low energy. Moreover, the new systems… Read More

"Ten-hut!" Attending the Signal Integrity Bootcamp

The engineering team for the design and analysis of a complex system consists of a diverse set of skills — with the increasing emphasis on both high-speed interface design and multi-domain power management, a critical constituent of the team is the group of signal integrity (SI) and power integrity (PI) engineers.

The training… Read More

Mentor gets Busy at DVCon

You’d expect Mentor to be covering a lot of bases at DVCon and you wouldn’t be wrong. They’re hosting tutorials, a lunch, papers, posters, there’s a panel and of course they’ll be on the exhibit floor. I’ll start with an important tutorial that you really should attend, Monday morning, on creating Portable Stimulus Models… Read More

CEO Interview: Srinath Anantharaman of ClioSoft

It will soon be 20 years since ClioSoft started its journey of selling design management software for the semiconductor industry. It was a slow start considering that designs were relatively small and only digital front-end designers had begun to realize the importance of version control and design management. With open source… Read More

Mentor Plays for Keeps in Emulation

EDA has always been a fiercely competitive market, no more so than in emulation where the clash of claims and counter-claims can leave those of us on the sidelines wondering who’s really on top. Sales are the obvious indicator but leadership there flips back and forth between product releases. That makes Mentor’s choice to play … Read More

Four Barriers to Using an SoC for IoT Projects

I often read about the large number of expected IoT design starts around the world, so I started to think about what the barriers are for launching this industry in order to meet the projections. One of my favorite IoT devices is the Garmin Edge 820, a computer for cyclists that has sensors for speed, cadence, power, heart rate, altitude… Read More

Aldec Rounds Out ALINT-PRO Checker

If there’s anyone out there who still doesn’t accept the importance of static RTL verification in the arsenal of functional verification methods, I haven’t met any recently. That wasn’t the case in my early days in this field. Back then I grew used to hearing “I don’t make mistakes in my RTL”, “I’ll catch that in simulation”, “My editor… Read More

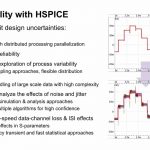

Using HSPICE StatEye to Tackle DDR4 Rail Jitter

The world is a risky place, according to Scott Wedge, Principal R&D Engineer at Synopsys, who presented at the Synopsys HSPICE SIG on Feb 2[SUP]nd[/SUP] in Santa Clara. Indeed, the world circuit designers face can be uncertain. Dealing with risk and departure from ideal was a main theme in the fascinating talks at this dinner… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center