It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Electronic Design Automation

Noise, The Need for Speed, and Machine Learning

Technology trends make the concerns with electronic noise a primary constraint that impacts many mainstream products, driving the need for “Design-for-Noise” practices. That is, scaling, and the associated reduction in the device operating voltage and current, in effect magnifies the relative importance of non-scalable… Read More

Dear Cadence: Calibre Didn’t Run Any Dracula Decks

After reading the Cadence blog post –“Dracula, Vampire, Assura, PVS: A Brief History” – Dr. Andrew Moore has written the below article where he helps readers get a sense as to what “the year of hell” was like, from one of the key individuals who lived it. Andrew also addresses and corrects some of the “urban legends”… Read More

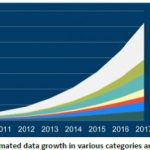

Data Center Explosion Push for Fast Adoption of 25G

The data center rack server market is estimated to growat a high Compound Annual Growth Rate (CAGR) of 20% to reach $90 billion by 2021. Such growth is due to the significantly rise in the number of connected devices, the growth in the volume of data per device and theneed for quick processing of high-volume data. Much of these data … Read More

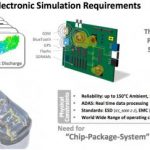

Simulating ADAS

Simulation is a broad technique spanning certainly digital logic and circuit simulation but also methods beyond these which are particularly relevant to ADAS design. In fact, much of the design of full ADAS systems begins and ends with these types of modeling. This is in part due to the need fully validate integrity and reliability… Read More

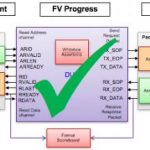

Quantifying Formal Coverage

Verification coverage is a tricky concept. Ideally a definition would measure against how many paths were tested of every possible path through the complete state graph, but that goal is unimaginably out of reach for any typical design. Instead we fall back on proxies for completeness, like hitting every line in the code. This … Read More

Smart & Connected Devices to Artificial Intelligence and Beyond

Last Friday I attended a breakfast seminar organized by SEMI in Hillsboro, Oregon with fascinating speakers from several high-tech companies: Qorvo, Intel, Oregon Angel Fund, Kimera, Moonshadow Mobile and Yole Development. I recalled that Qorvo was created from the merger of TriQuint Semiconductor and RF Micro Devices back… Read More

Scaling Enterprise Potential with ClioSoft’s designHUB platform

I’ve had the privilege over the years to be a part of a lot of great companies, teams and projects. Some of these efforts were quite successful while others were not. It begs the question of why is it so hard to enable design reuse and capture the untapped potential of the collective intelligence within our companies? Up till now, companies… Read More

Webinar – Next Generation DDRM Needs, Solutions

I’m a believer in product life-cycle management (PLM) for semiconductor design. It’s not an attention-grabbing topic like faster verification or improved PPA in implementation, but now massive IP-based design is routine, IP’s are sourced from multiple suppliers each cycling though multiple revisions and now that design … Read More

An Overview of Jama Software in the Semiconductor Industry

Portland, Oregon is a hotbed of innovation for software development companies and I tend to scan the headlines of my local newspaper the Oregonian, which is where I first started to read about Jama Software a few years back. Curiosity and opportunity drove me to meet with Trevor Smith of Jama in their Portland office. We chatted for… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center