You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Introduction

For many years, I pondered the ultimate future of EDA. Companies such as Oracle, SAP and Dassault provide a huge array of enabling software infrastructure for the enterprise, including product design, mechanical design, project management and materials sourcing. But not for the all-important tasks of chip and… Read More

Arm and Mentor Recently announced that the Arm Design Reviews program now offers Mentor help in verification design reviews. I talked to Paul Williams (Sr Consultant and Verification Practice Lead at Mentor Graphics) and Peter Lewin (Dir. Mktg at Arm Partner Enablement Group) to get more insight into Arm Design Services, particularly… Read More

SLM. It’s a TLA (three-letter acronym) that you’ll be hearing more about. It stands for silicon lifecycle management and it has the potential of re-defining the role of EDA in the entire electronics ecosystem. A working definition of SLM is “monitoring, analysis and optimization of semiconductor devices as they are designed,… Read More

Cadence made waves a while back with its innovative Clarity 3D Solver, a FEM solver for near field EM analysis. Now they are shaking things up with their new far field Clarity 3D Transient Solver. System level EMI and EMC analysis has often exceeded the limits of simulation tools, leading to expensive and time-consuming prototype… Read More

Anyone who frequents SemiWiki will likely know Moore’s Law. The prediction made by Gordon Moore over 50 years ago regarding the relentless increase in transistor density and reduction in cost has tracked well for a very, very long time. In recent years, there has been spirited discussion about the end of Moore’s Law. This is a discussion… Read More

Hands down, without a doubt, the most interesting CEO in semiconductors is Lip-Bu Tan, founder of Walden Capitol and current CEO of Cadence Design Systems. If you want to talk about a man with a plan it’s Lip-Bu Tan.

Before we get into the fireside chat between Tom Caufield and Lip-Bu at the GTC 2020 Virtual event let’s do a quick biography:… Read More

Covering configurable systems is a challenge. What’s a good strategy to pick a small subset of settings and still get high confidence in coverage? Paul Cunningham (GM, Verification at Cadence), Jim Hogan and I continue our series on research ideas, here an idea from software testing which should also apply to hardware. Feel free… Read More

MIPI may have started out as a standard for mobile phones, but it has become very important for connecting cameras and displays in a wide range of other things such as cameras, computers, drones, VR glasses, IoT devices and cars. Along the way it has matured by adding important features to support new applications. Now when we talk… Read More

The semiconductor industry is fiercely competitive. This is widely known by the SemiWiki community. When it comes to critical design parameters such as power, performance or area you’re either in the envelope that defines the market or you’re not a player. Yield management has a similar impact. Those who can stay ahead of the yield… Read More

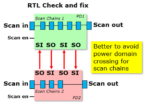

In the early days of Atrenta I met with Ralph Marlett, a distinguished test expert with many years of experience at Zuken and Recal Redac. He talked me into believing we could do meaningful static analysis for DFT-friendliness at RTL. His work with us really opened my eyes to the challenges that test groups face in integrating their… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era