Workflows allow the world to function. The orderly process of sequencing tasks and automating handoffs creates tremendous potential for efficiency and error avoidance. As they say, time is money and workflows can save a lot of time. The principle applies in all kinds of industries. If you design chips for a living, you’re very … Read More

Electronic Design Automation

Verification IP for Systems? It’s Not What You Think.

When I think of verification IP (VIP), I think of something closely tied to a protocol standard – AMBA, MIPI or DDR for example. Something that will generate traffic and run protocol compliance checks, to verify correct operation of an IP or as a model to use in SoC verification. What would a VIP for systems be? Systems support multiple… Read More

The Gold Standard for Electromagnetic Analysis

Ansys HFSS has been the world’s trusted gold standard for electromagnetic analysis for many years. As chip designs get bigger and more complex many users report that they’re extremely happy with the gold standard accuracy of HFSS but wish it would run faster. Fortunately Ansys has introduced many capabilities to HFSS over the… Read More

Verifying PCIe 5.0 with PLDA, Avery and Aldec

Mike Gianfagna, a fellow SemiWiki blogger and a one-time colleague at Atrenta shared a useful piece of marketing advice. If your company is not the biggest fish in the pond and you want to appear more significant, team up with other companies to put on an event, say a webinar. Pick your partners so that you can jointly offer a larger,… Read More

SkillCAD Adds Powerful Editing Commands to Virtuoso

Despite the large role of place and route in IC design, there will always be a need for custom layout design. This is particularly true in radio frequency (RF), power management (PM) and power amplifier (PA) circuits, among others. Cadence Virtuoso is by far the leading tool for creating these custom designs. Virtuoso has a sophisticated… Read More

Free Webinar on SPICE Simulation

The world of SPICE simulators is one filled with compromises. Typically, it is possible to choose the highest accuracy and pay a performance and capacity penalty, or to choose high speed and capacity but give up accuracy in the process. Many semiconductor companies have been turning to Primarius Technologies to help escape these… Read More

Mentor User2User Virtual Event 2020!

Now that we have gone virtual, life has never been easier, for me anyway. There are literally events every day beamed into my living room. The question is which should I attend? The answer is I should attend the ones with the most customer-based content, which is what User2User is all about. I will miss attending this one live as it was… Read More

Automating the Design of Flat Panel Displays

I’ve used OLED (Organic Light-Emitting Diode) displays for many years in my monitors, laptops, tablets, e-readers and smart phones; and knew that the AMOLED (Active-Matrix OLED) displays used thin-film transistor technology where each pixel can be controlled, but I hadn’t considered the actual design process… Read More

How ML Enables Cadence Digital Tools to Deliver Better PPA

There has been a lot written about artificial intelligence/machine learning (AI/ML) and its application in the Cadence digital design flow. Most recently, I covered significant verification efficiency improvements in Xcellium ML. A recent digital-themed white paper from Cadence takes a broader look at the impact of ML on… Read More

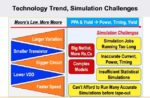

ASIC and FPGA Design and Verification Trends 2020

Harry Foster and I started in semiconductors at the same time so it was great to reminisce while talking about the latest Wilson Research Group Functional Verification Trend reports. Before I get into the reports lets talk about Harry who is a verification superstar:

Harry is Chief Scientist Verification for the Design Verification… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era