Debugging an IC is never much fun because of all the file formats used, the levels of hierarchy and just the sheer design size, so when an EDA tool comes around that allows me to get my debugging done quicker, then I take notice and give it a look. I was already familiar with debugging SPICE netlists using a tool called SPICEVision Pro,… Read More

Electronic Design Automation

Webinar: OCV and Timing Closure Sign-off by Silvaco on Oct 10 at 10AM

The old adage that goes the one constant thing you can always count on is change, could easily be reworded for semiconductor design to say the one constant thing you can count on is variation. This is doubly true. Not only is variation, in all its forms, a constant factor in design, additionally the methods of analyzing and dealing … Read More

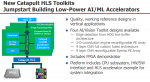

AI Hardware Summit, Report #2: Lowering Power at the Edge with HLS

I previously wrote a blog about a session from Day 1 of the AI Hardware Summit at the Computer History Museum in Mountain View, CA, held just last week. From Day 2, I want to delve into this presentation by Bryan Bowyer, Director of Engineering, Digital Design & Implementation Solutions Division at Mentor, a Siemens Business.… Read More

Virtually Verifying SSD Controllers

Solid State Drives (SSDs) are rapidly gaining popularity for storage in many applications, in gigabytes of storage in lightweight laptops to tens to hundreds of terabyte drives in datacenters. SSDs are intrinsically faster, quieter and lower-power than their hard disk-drive (HDD) equivalents, with roughly similar lifetimes,… Read More

Webinar of Recent NCTU CDM/ESD Keynote Talk by Dundar Dumlugol – Thursday September 26th

With many design teams still searching for an effective means of identifying Charged Device Model (CDM) issues early in the design process, it comes as no surprise that events on this topic generate a lot of interest and are well attended. In July Magwel’s CEO Dr. Dundar Dumlugol had the honor of being invited by Professor Ming-Dou… Read More

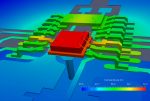

Cadence Celsius Heats Up 3D System-Level Electro-Thermal Modeling Market

A few years back people were saying that the “EDA” problem was solved and that design tools had become commodity. At the same time people hailed ADAS, smart homes, mobile communication and AI as the frontiers of electronics. Perhaps it could be said that layout tools, routers, placers, and circuit simulators had largely matured… Read More

Speeding Up Physical Failure Analysis (PFA)

The cost of an IC depends on many factors like: NRE, masks, fabrication, testing, packaging. Product engineers are tasked with testing each part and understanding what exactly is limiting the yields. Every company has a methodology for Physical Failure Analysis (PFA), and the challenge is to make this process as quick as possible,… Read More

WEBINAR: AI-Powered Automated Timing Arc Prediction for AMS IP’s

A directed approach to reduce Risk and improve Quality

Safety and reliability are critical for most applications of integrated circuits (ICs) today. Even more so when they serve markets like ADAS, autonomous driving, healthcare and aeronautics where they are paramount. Safety and reliability transcend all levels of an integrated… Read More

Automatic Documentation Generation for RTL Design and Verification

Ask any hardware or software engineer working on a product, and they will tell you that writing documentation is a pain. Customers have high expectations for user manuals and reference guides, usually requiring a team of technical writers to satisfy their requirements. In order to meet time-to-market deadlines, documentation… Read More

WEBINAR: Reusing Your IPs & PDKs Successfully With Cadence® Virtuoso®

I recently wrote about a ClioSoft® study with Google on using cloud platforms for EDA design and the importance of using persistent storage when doing that. ClioSoft will again be sharing important information on design productivity in the upcoming webinar, Reusing Your IPs & PDKs Successfully With Cadence® Virtuoso®. … Read More

TSMC N3 Process Technology Wiki