Predictions in technology adoption often hinge on a delicate balance between technical feasibility and market dynamics. While business considerations play a pivotal role, the technical category reasons for the success or failure of a prediction are more tangible and often easier to identify—if scrutinized with care. However,… Read More

ML and Multiphysics Corral 3D and HBM

3D design with high-bandwidth memory stacks (HBM) has become essential for leading edge semiconductor systems in multiple applications. Hyperscalers depend on large AI accelerator cores supported by 100GB or more of in-package HBM to handle trillion parameter AI models. Autonomous Drive (AD) vehicles may handle smaller … Read More

Accelerating Automotive SoC Design with Chiplets

The automotive industry is evolving rapidly with the increasing demand for intelligent, connected, and autonomous vehicles. Central to this transformation are System-on-Chip (SoC) designs, which integrate multiple processing units into a single chip for managing everything from safety systems to in-car entertainment.… Read More

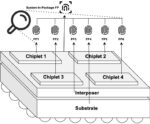

Scaling AI Data Centers: The Role of Chiplets and Connectivity

Artificial intelligence (AI) has revolutionized data center infrastructure, requiring a reimagining of computational, memory, and connectivity technologies. Meeting the increasing demand for high performance and efficiency in AI workloads has led to the emergence of innovative solutions, including chiplets, advanced… Read More

Defect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRI

In the quest to secure the authenticity and ownership of advanced integrated circuit (IC) packages, a novel approach has been introduced in this paper that capitalizes on the inherent physical discrepancies within these components. This method, distinct from traditional strategies like physical unclonable functions (PUFs)… Read More

How AI is Redefining Data Center Infrastructure: Key Innovations for the Future

Artificial intelligence (AI) is driving a transformation in data center infrastructure, necessitating cutting-edge technologies to meet the growing demands of AI workloads. As AI systems scale up and out, next-gen compute servers, switches, optical-electrical links, and flexible, redundant networking solutions are … Read More

Maximizing 3DIC Design Productivity with 3DBlox: A Look at TSMC’s Progress and Innovations in 2024

At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

Synopsys and TSMC Pave the Path for Trillion-Transistor AI and Multi-Die Chip Design

Synopsys made significant announcements during the recent TSMC OIP Ecosystem Forum, showcasing a range of cutting-edge solutions designed to address the growing complexities in semiconductor design. With a strong emphasis on enabling next-generation chip architectures, Synopsys introduced both new technologies and … Read More

5 Expectations for the Memory Markets in 2025

TechInsights has a new memory report that is worth a look. It is free if you are a registered member which I am. HBM is of great interest and there is a section on emerging and embedded memories for chip designers. Even though I am more of a logic person, memory is an important part of the semiconductor industry. In fact, logic and memory

Collaboration Required to Maximize ASIC Chiplet Value

It is a well-known fact that chiplets provide several advantages over traditional monolithic chips. Despite these benefits, the transition to a chiplet-based design paradigm presents challenges that need coordinated efforts across the industry. In essence, collaborative efforts among various players involved are not … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?