It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability and traction control. A failure of any of these systems can endanger human life or safety. As a result, there is a focus on implementing ISO 26262 across the board in products aimed at the automotive market. At the same time there is increasing complexity in many chips coupled with utilization of more advanced nodes, both of which have major implications for safety.

Meeting the requirements of ISO 26262 includes activity at every stage of chip development, starting during specification and going right through to design, manufacture, test and out into the field. Test in particular plays a significant role in implementing ISO 26262. After all, failure detection is essential. I recently had the opportunity to read an interesting white paper by Mentor on how their Tessent test tools can be helpful in meeting ISO 26262 requirements. The paper talks about three areas where test has evolved to meet the needs of ISO 26262 in the automotive market. They are on-line testing during chip and system operation, new types of testing to comprehensively detect a wider range of failures and making analog circuits testable.

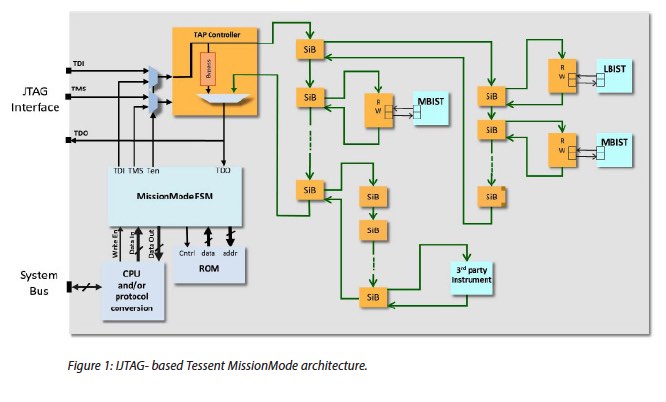

Beyond just testing chips at the time of manufacture, or perhaps at power-on, ISO 26262 calls for continuous and periodic testing. Fortunately, many pieces of the manufacturing test elements embedded in the chip can be used for testing during operation. Mentor’s Tessent MissionMode architecture provides test access to individual IP and memory elements during chip operation. Tessent MissionMode in turn can be driven by previously stored test vectors or externally through the system bus. IEEE 1687 IJTAG is used to wrap IP blocks for test and can be accessed by Tessent Mission Mode. However, Tessent MissionMode can also access any other type of test interface, as needed.

One intriguing capability of Tessent MissionMode is non-destructive memory BIST. Testing is done in short busts, accessing small ranges of memory. This is non-destructive because the memory contents are saved and restored, making the test operation transparent to the running system. Because of the low overhead of each individual burst, this testing can cover the entire memory piecewise without contention with system operation.

Mentor also has some innovations in Logic BIST, where they apply a hybrid solution that utilizes ATPG and compression in Logic BIST, which can be used during power-on, power-off or for on-line testing. The benefits of this hybrid approach include area savings, because the scan chains are utilized for tester runs and self-testing. An issue with BIST during functional operation is increased power consumption due to high toggle rates. Tessent offers the ability to scale toggle rates to limit transitions, trading this off with some increase in pattern count.

The Mentor paper on Tessent also discusses how test methodologies have to move beyond ‘netlist’ level faults and add checking for cell level issues. The paper says that by some estimates cell level faults account for almost half of all circuit level defects. Traditional fault models are not targeting these faults. This means that many of these defects are found only by chance. Tessent now includes a Cell-aware methodology that digs deeper into the circuits to look for these harder to find defects.

Despite the well-established methodologies for digital fault analysis, analog designs have gone without until now. Tessent DefectSimfault simulator is the first commercial solution for analog designs. A key enabler is the development of analog simulation tools that run orders of magnitudes faster than before. It is now possible to efficiently look at parametric variations to help find defects. The paper describes some interesting techniques that are being applied to make analog test more effective. A majority of field failures in mixed signal chips occur due to issues with the analog portion. Automated analog test generation will be a tremendous help in securing ISO2626 compliance in mixed signal chips.

With every innovation in chip design, there comes an added challenge for test. The added requirements for meeting ISO 26262 add even more difficulty in the test domain. However, this Mentor white paper on the topic of how Tessent features can be applied shows that with innovation the test challenges for automotive systems can be more easily addressed. It also points out once again how the demands of developing automotive electronics is providing motivation for many of the current improvements in electronic design. The full white paper, entitled “MEETING ISO 26262 REQUIREMENTS USING TESSENT IC TEST SOLUTIONS” makes good reading and is easily available from the Mentor website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.