Semiconductor technology is among the most complex of technologies and the semiconductor industry is among the most demanding of industries. Yet the ecosystem has delivered incredible advances over the last six decades from which the world has benefitted tremendously. Yes, of course, the markets want that break-neck speed… Read More

Tag: test

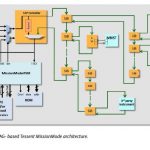

Balancing Test Requirements with SOC Security

Typically, there is an existential rift between the on-chip access requirements for test and the need for security in SoCs. Using traditional deterministic scan techniques has meant opening up full read and write access to the flops in a design through the scan chains. Having this kind of access easily defeats the best designed… Read More

Tessent Streaming Scan Network Brings Hierarchical Scan Test into the Modern Age

Remember when you had to use dial up internet or parallel printer cables connected directly to the printer to print something? Well even if you don’t remember these things, you know that now there is a better way. Regrettably, the prevalent methods used for hierarchical Design for Test (DFT) still look at lot like this – SoC level … Read More

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More

ITC shines light on new Mentor Test announcements

The 50th International Test Conference was just held in Washington DC, where papers, sessions, workshops and announcements addressing the increasing complexity and expanding use of semiconductors showed that innovations in test are crucial to design and product success. Test methodologies and even the scope of test have … Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

Mentor’s Busy ITC and Major Test Product Updates

In conjunction with the 2018 International Test Conference, Mentor has several interesting test announcements. They also have a busy round of technical activities, including a number of technical papers, presentations, tutorials and a poster from a major customer about using Mentor. I’d like to touch on the two product related… Read More

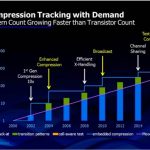

Time is Money, Especially when Testing ICs

Semiconductor companies are looking for ways to keep their business profitable by managing expenses on both the design and test side of electronic products, which is quite the challenge as the trends show increases in test pattern count and therefore test costs. Scan compression is a well-known technique first created over 15… Read More

Virtual Modeling Drives Auto Systems TTM

The electronics market for automotive applications is distinguished by multiple factors. This is a very fast growing market – electronics now account for 40% of a car’s cost, up from 20% just 10 years ago. New technologies are gaining acceptance, for greener and safer operation and for a more satisfying consumer experience. Platforms… Read More

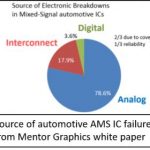

Mentor DefectSim Seen as Breakthrough for AMS Test

For decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs.… Read More