The 50th International Test Conference was just held in Washington DC, where papers, sessions, workshops and announcements addressing the increasing complexity and expanding use of semiconductors showed that innovations in test are crucial to design and product success. Test methodologies and even the scope of test have expanded over the lifetime of this event. If test methods had grown linearly with design size and complexity, today’s massive designs would be effectively untestable. At the same time test activity has moved from being a manufacturing step into something necessary throughout the life of the design in many applications.

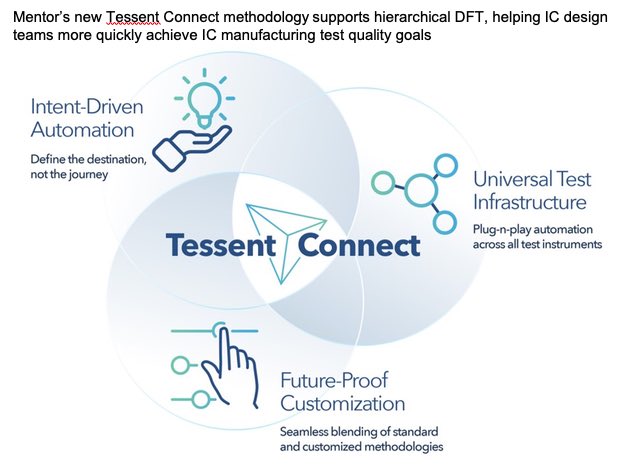

The one major message here is that the scale and scope of test is expanding, and the industry is working to keep up and track these changes. Evidence of this is provided in announcements by Mentor during the ITC. The first of these deals with Mentor’s Tessent Connect, which provides much needed automation in hooking up hierarchical test elements. The benefits of hierarchical test are well understood. Each core can have test added during design. The result is easier scan insertion, better observability and quicker test pattern generation. Also, top level resources are conserved by applying IJTAG based on IEEE 1687. When there are design iterations, and there always are, only the blocks affected need to have test changes.

The downside is that a lot of manual effort is required to connect each core for the chip level test implementation. Tessent Connect helps automate the process of making these connections. Designers using Tessent Connect work at a higher level of abstraction that focuses on intent rather than the details of stringing together individual wires. This is useful especially when working in cross team environments. To help facilitate its adoption Mentor has also created a quickstart program for Tessent Connect to help with flow assessment and provide implementation services.

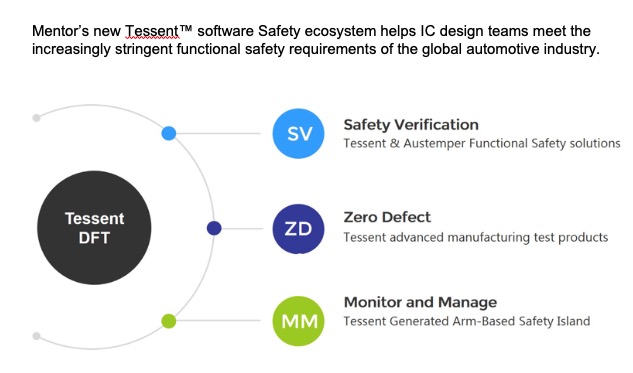

The second Mentor announcement at ITC was the introduction of the Tessent Safety ecosystem. They describe it as a comprehensive portfolio of best-in-class automotive IC test solutions from Mentor and links to its industry-leading partners. In applications such as automobiles, test now plays a major role during system operation. This has led to expanded use of Logic BIST, which can be used in chips throughout their life. For instance, ISO 26262 calls for regular and repeated testing of automotive systems during operation to detect failures so corrective action can be taken. These tests must be performed quickly and in such a way as to not interfere with overall system operation.

Mentor’s Tessent Safety ensures that tests are non-destructive to system operation and that tests are run much faster than alternative approaches. One new technology they are using is called Observation Scan Technology (OST), which includes IP that can be inserted selectively to boost observability. This translates into a 10X improvement in performance and helps reduce layout congestion. Mentor is also adding close links to their Austemper SafetyScope and KaleidoScope products.

Mentor is participating in the ARM Functional Safety Partnership Program, leveraging ARM Safety Ready IP, like the Cortex-R52 processor. There are many other aspects to the Tessent Safety ecosystem. A partial list includes analog test capabilities, memory BIST – at RTL or gate level, automotive grade ATPG and transistor level defect simulation. The level of rigor in the Tessent Safety ecosystem comes as no surprise given their long experience with automotive applications and their test expertise. The Tessent Connect and Tessent Safety announcements from this year’s ITC are available on the Mentor website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.