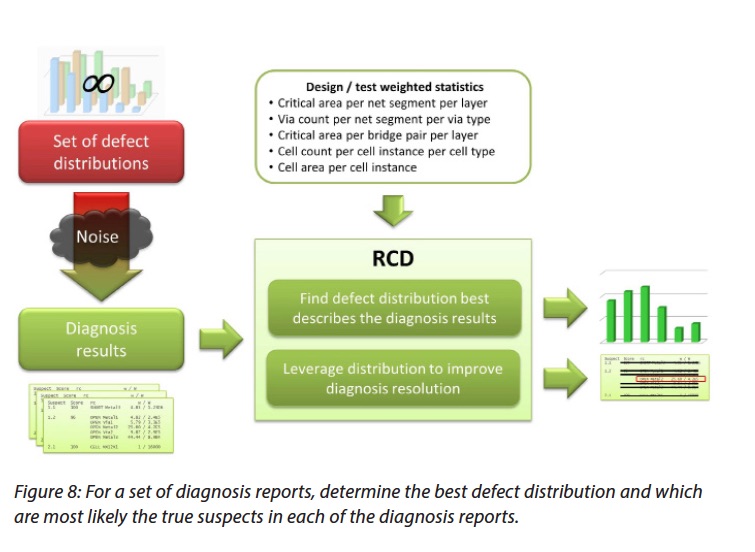

Naturally, chips that fail test are a curse, however with the advent of Scan Logic Diagnosis these failures can become a blessing in disguise. Through this technique information gleaned from multiple tester runs can help pin down the locations of defects. Initially tools that did Scan Logic Diagnosis relied on the netlist to filter… Read More

Author: Tom Simon

Automotive is setting the goalposts for next generation designs

Automotive applications are having a tremendous influence on semiconductor design. This influence is coming from innovations in cloud computing, artificial intelligence, communications, sensors that all serve the requirements of the automotive market. It should come as no surprise that ADAS and autonomous driving are … Read More

Know what 5G is? You’re probably wrong

If you think the transition to 5G will be anything like the transitions before it to 3G or 4G, you are in for a big surprise. Not only will the transition take longer than either of the previous transitions, its ramifications will spread far beyond cell phones and into other areas such as automobiles, AI, healthcare, and commerce. … Read More

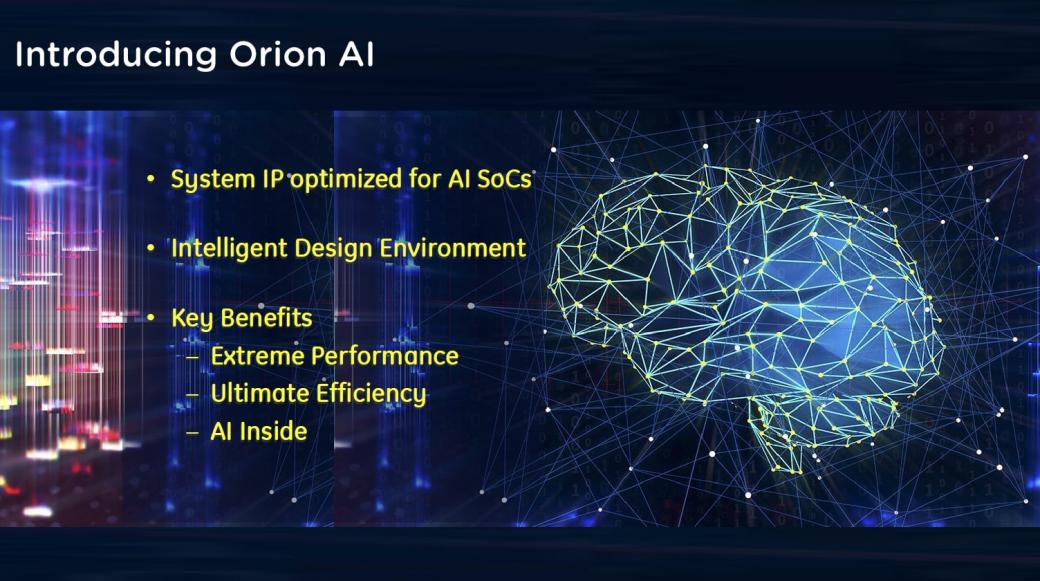

Leveraging AI to help build AI SOCs

When I first started working in the semiconductor industry back in 1982, I realized that there was a race going on between the complexity of the system being designed and the capabilities of the technology in the tools and systems used to design them. The technology used to design the next generation of hardware was always lagging… Read More

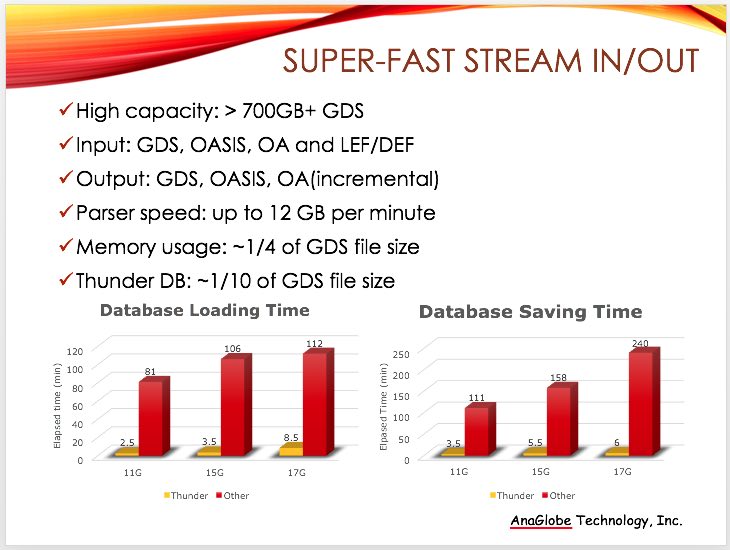

Billion Transistor Designs Need Faster Full Chip Tools

During the design cycle as tape out approaches, time pressure usually goes up dramatically. To make matters worse the design itself is much larger, because all the block level work is done and there is a requirement to work with the entire database. It feels like it’s time to put aside the garden trowel and start using a steam shovel.… Read More

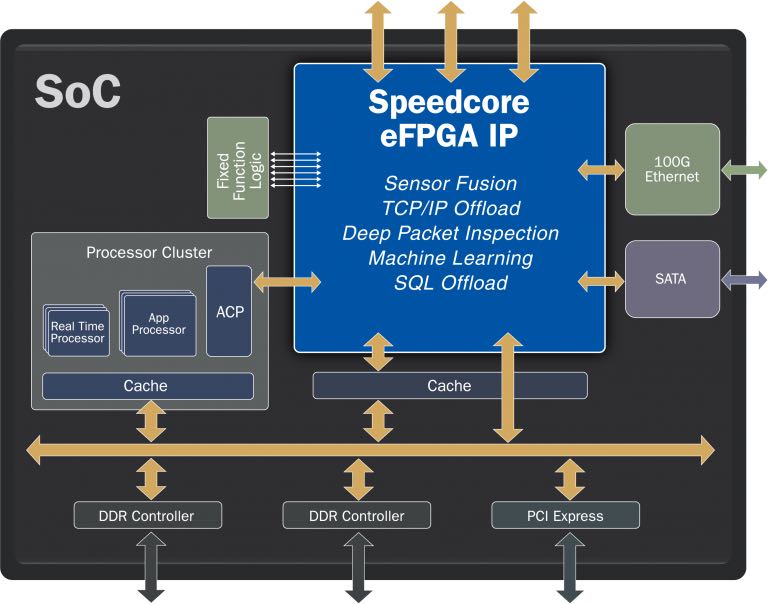

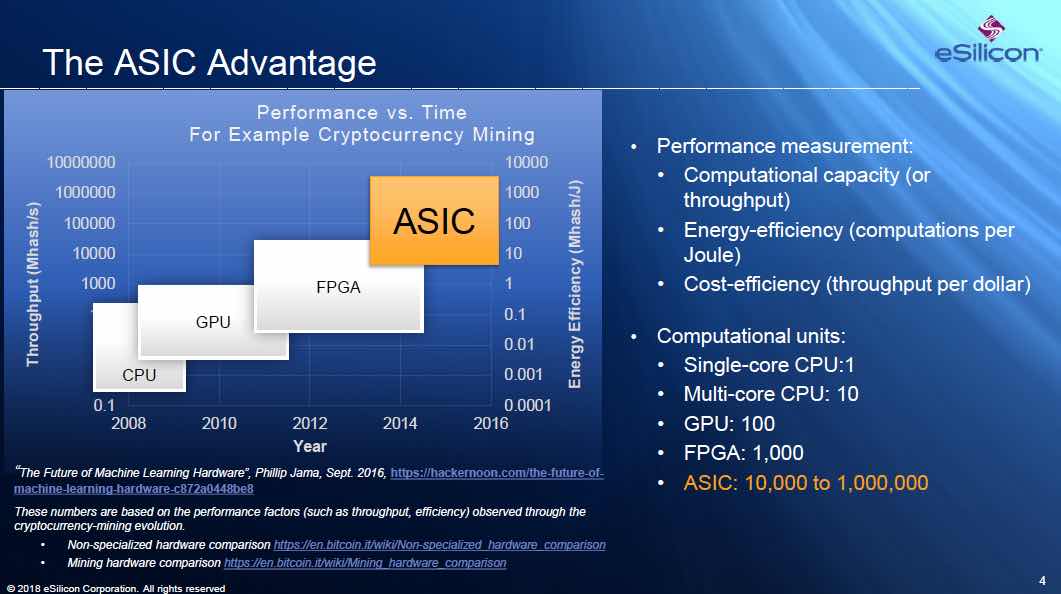

Being Intelligent about AI ASICs

The progression from CPU to GPU, FPGA and then ASIC affords an increase in throughput and performance, but comes at the price of decreasing flexibility and generality. Like most new areas of endeavor in computing, artificial intelligence (AI) began with implementations based on CPU’s and software. And, as have so many other applications,… Read More

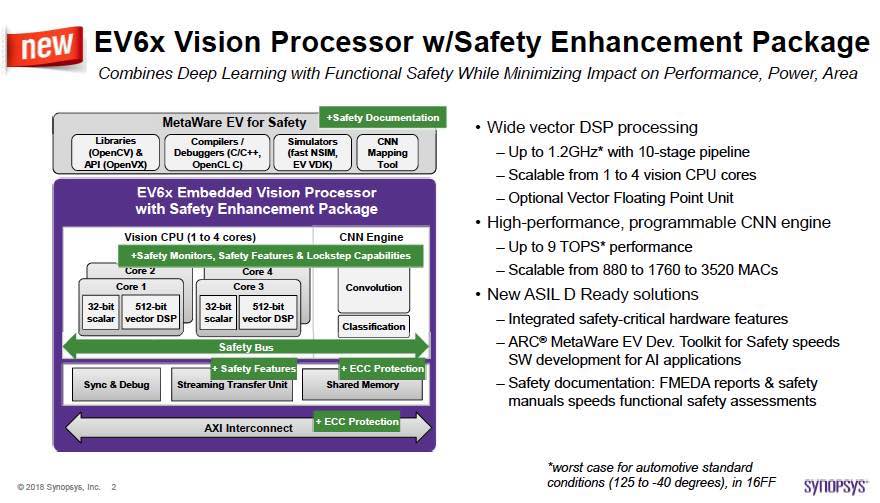

ISO 26262 First – ASIL-D Ready Vision Processor IP Available

Synopsys made a pretty major announcement regarding their new ASIL-B,C and D ready embedded vision processor IP. This matters because you cannot bolt on the design elements and features needed to achieve these ASIL levels later, and this IP is absolutely necessary for ADAS systems and other critical safety systems in automobiles.… Read More

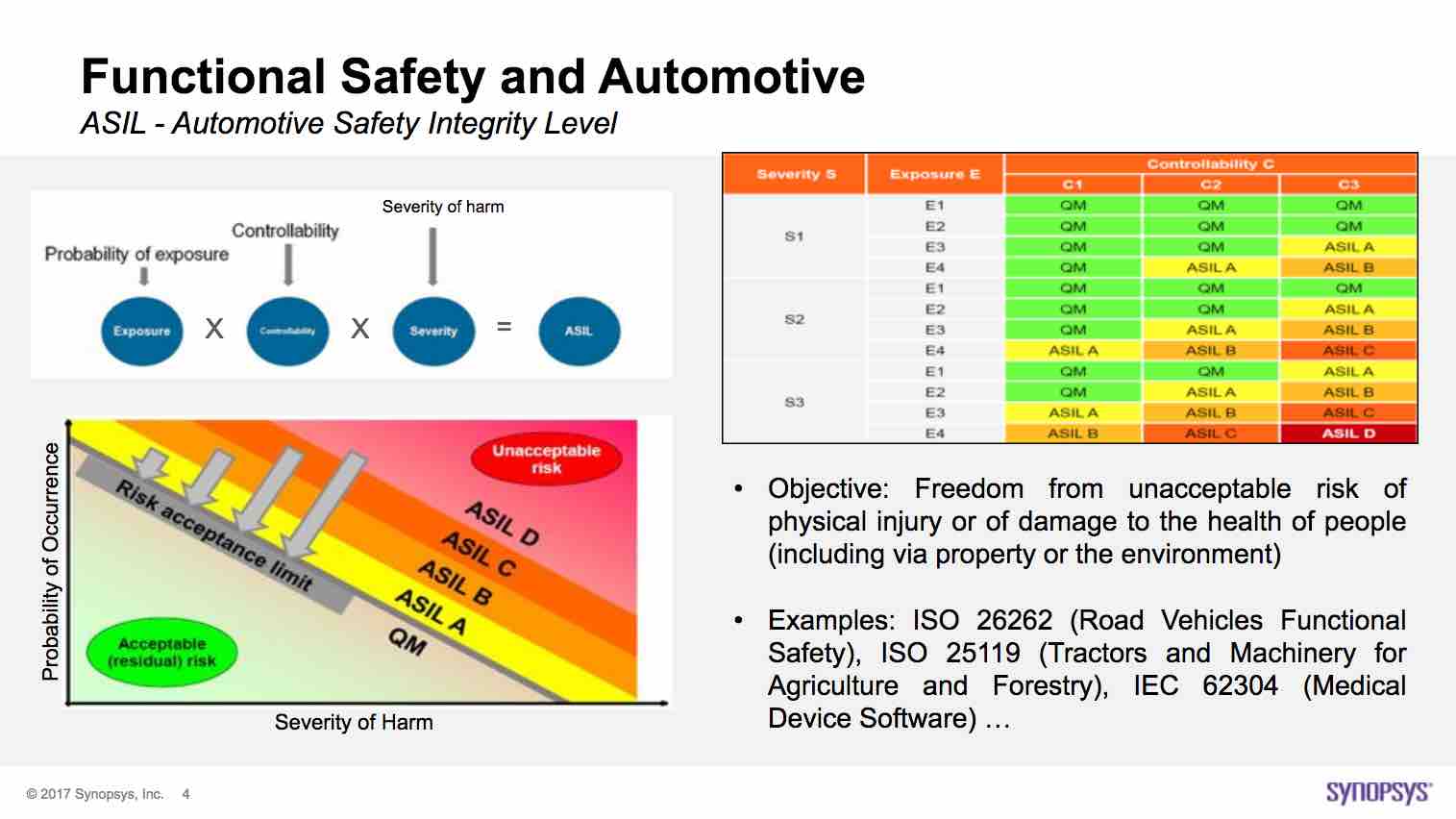

Functional Safety is a Driving Topic for ISO 26262

When I was young, functional safety for automobiles consisted of checking tread depth and replacing belts and hoses before long trips. I’ll confess that this was a long time ago. Though even not that long ago, the only way you found out about failing systems was going to the mechanic and having them hook up a reader to the OBD port. Or,… Read More

Machine Learning Drives Transformation of Semiconductor Design

Machine learning is transforming how information processing works and what it can accomplish. The push to design hardware and networks to support machine learning applications is affecting every aspect of the semiconductor industry. In a video recently published by Synopsys, Navraj Nandra, Sr. Director of Marketing, takes… Read More

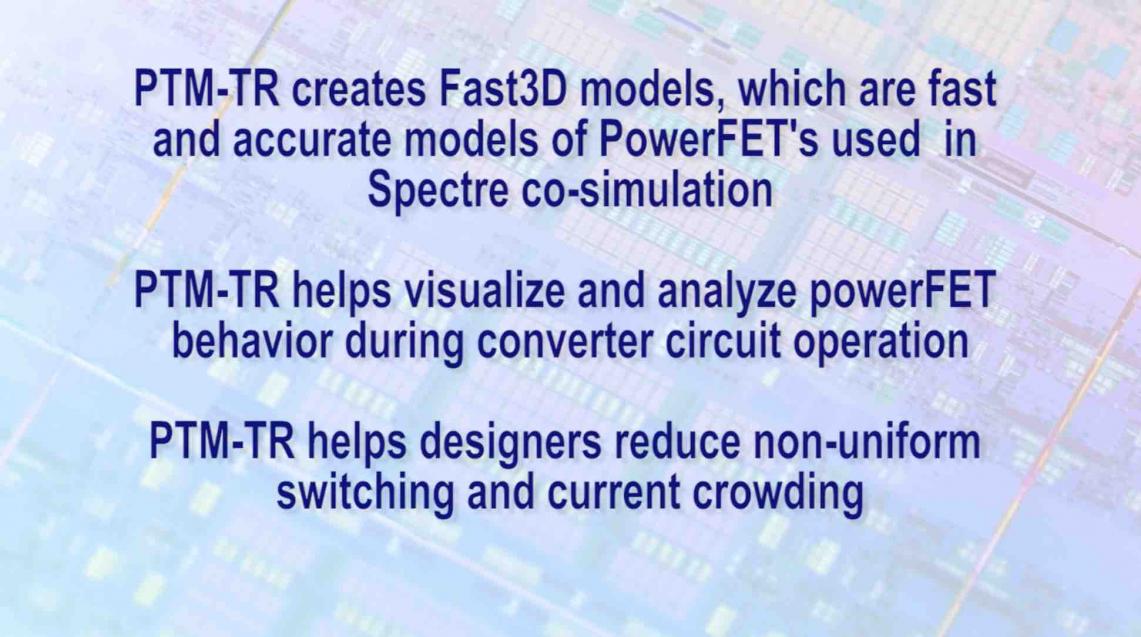

Converter Circuit Optimization Gets Powerful New Tool

DC converter circuit efficiency can have a big effect on the battery life of mobile devices. It also can affect power efficiency for wall-power operated circuits. Even before parasitics are factored in, converter circuit designers have a lot of issues to contend with. Optimizing circuit operation is essential for giving consumers… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification