During the 1940s when aerospace engineers were attempting to break the sound barrier for the first time, they were confronting a slew of new technical issues that had never been dealt with before, and in some cases never seen before. In subsonic flight airflow was predictable and well understood. In crossing the sound barrier, … Read More

Author: Tom Simon

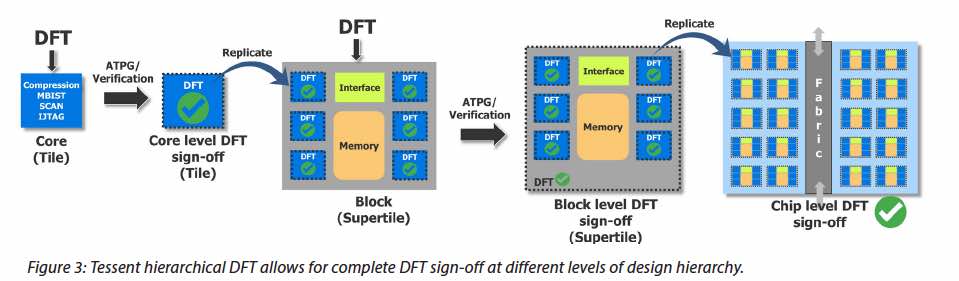

How to be Smart About DFT for AI Chips

We have entered the age of AI specific processors, where specialized silicon is being produced to tackle the compute needs of AI. Whether they use GPUs, embedded programmable logic or specialized CPUs, many AI chips are based on parallel processing. This makes sense because of the parallel nature of AI computing. As a result, in… Read More

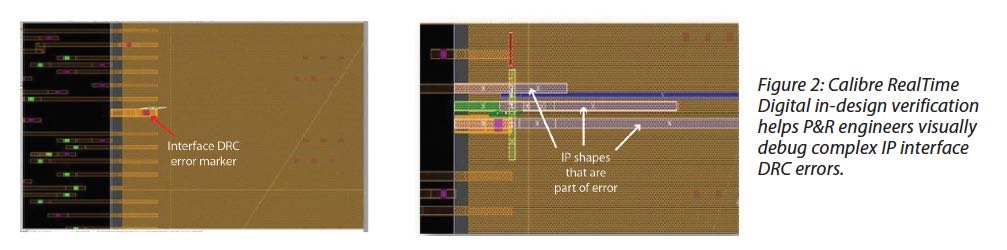

Qualcomm Attests Benefits of Mentor’s RealTime DRC for P&R

When floor planning (FP) and place & route (P&R) tools took over from custom layout tools for standard cell based designs, life became a lot better for designers of large digital chips. The beauty of the new flows was that all the internals of the standard cells and many IP blocks were hidden from view, lightening the load … Read More

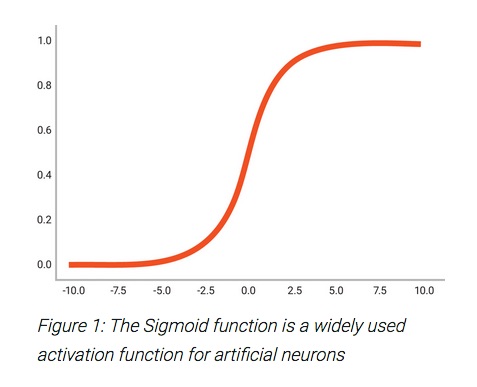

Mathematics are Hard – That is Why AI Needs Mathematics Hardware

The field of artificial intelligence has relied on heavy inspiration from the world of natural intelligence, such as the human mind, to build working systems that can learn and act on new information based on that learning. In natural networks, neurons do the work, deciding when to fire based on huge numbers of inputs. The relationship… Read More

At Last, Package and Chip integration for RF Design

It seems that it has always been that there were packages and ICs, and in the design tool world “never the twain shall meet”. The tools for designing packages were completely separate from the tools used to design IC’s. This was so profoundly true that even after Cadence merged with Valid Logic back in the early 90’s, their Allegro … Read More

The Ups and Downs of Google Assistant Mini

On Star Trek when they asked the computer to do something, they never heard it say “Sorry, you have no photon torpedoes connected to your account”. However, this sort of thing is something that happens at my house when I forget the exact name of a specific light. How did I get here?

I was reluctant to buy a “home assistant” for all the reasons… Read More

Designing a fully digitally controlled DC-DC buck converter

One of the unsung heroes of our digital world is the modest voltage converter. Batteries and wired power sources rarely match up with the supply needs for advanced ICs. Leading edge ICs have multiple voltage domains and very often, as in the case of processors, use dynamic voltage scaling to help conserve power. Looking at where … Read More

Ethernet Enhancements Enable Efficiencies

Up until 2016, provisioning Ethernet networks was a little bit like buying hot dogs and hot dog buns, in that you could not always match up the quantities to get the most efficient configuration. That dramatically changed when the specification for Ethernet FlexE was adopted by the Optical Internetworking Forum as OIF-FLEXE-01.0.… Read More

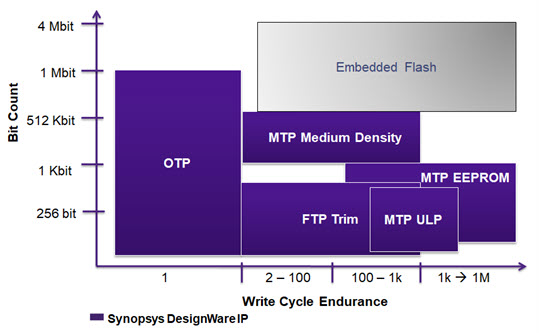

Synopsys Offers Smooth Sailing for OTP NVM

Nobody likes drama. Wait, let me narrow that down a bit. Chip designers really hate drama. They live in a world of risk and uncertainty, a world that tool and IP vendors spend considerable resources trying to make safer and more rational. It’s notable just how ironic that Sidense and Kilopass were duking out patent litigation in the… Read More

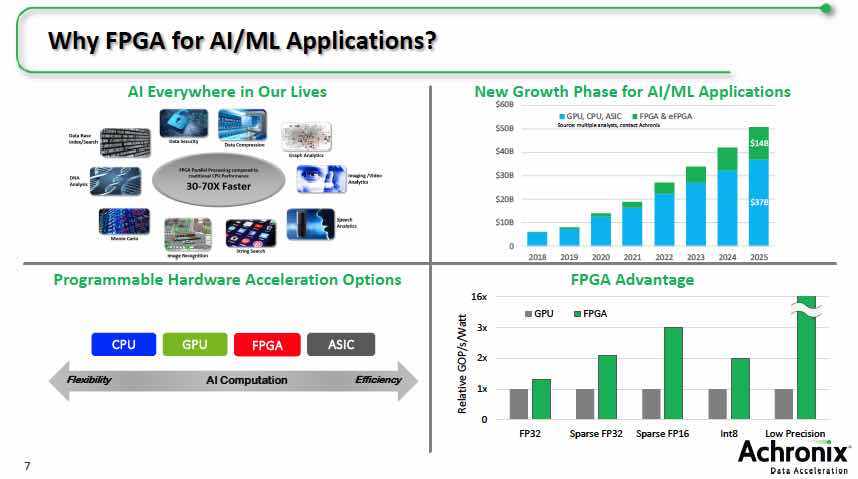

Embeddable FPGA Fabric on TSMC 7nm

With their current line-up of embeddable and discrete FPGA products, Achronix has made a big impact on their markets. They started with their Speedster FPGA standard products, and then essentially created a brand-new market for embeddable FPGA IP cores. They have just announced a new generation of their Speedcore embeddable… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification