Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

Author: Pawan Fangaria

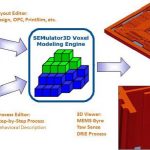

Quick MEMS Development Through Virtual Fabrication

The design and manufacture of MEMS is very different and in many ways more complex process than even the most advanced ICs. MEMS involve multiple degrees of freedom (i.e. the device to exhibit different characteristics under different physical state, motion or mechanics), making fabrication of MEMS extremely complex; and hence… Read More

Smart Watch, Phone, Phablet, Tablet, Thin Notebook…?

There are more, but wait a while, from this set which ones do you need? Or let me ask the question differently (I know you may like something impulsively and have money to buy), which ones do you want to buy and own? Still confused? I guess what you need, you already have, but you want to change it for something new and different. While I … Read More

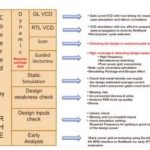

Highest Test Quality in Shortest Time – It’s Possible!

Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC.… Read More

Semicon Technology Advancement – A View From IEDM

As I see the semiconductor industry going through significant changes and advances, yet ironically plagued by a growing perception that the pace of scaling is slowing, I was inclined to take a peek into what the industry experts say about the state of the industry and the future of Moore’s Law. Fortunately, at last week’s International… Read More

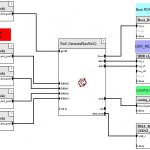

Taming The Interconnect In Real World For SoCs

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

What Makes A Designer’s Day? A Bottleneck Solved!

In an environment of SoCs with tough targets of multiple functionalities, smallest size, lowest power and fastest performance to achieve within a limited design cycle window in order to meet the rigid time-to-market requirements, any day spent without success becomes very frustrating for a designer. Especially during tape-out… Read More

Cadence & ARM Optimize Complex SoC Performance

Now a day, a SoC can be highly complex, having 100s of IPs performing various functionalities along with multi-core CPUs on it. Managing power, performance and area of the overall semiconductor design in the SoC becomes an extremely challenging task. Even if the IPs and various design blocks are highly optimized within themselves,… Read More

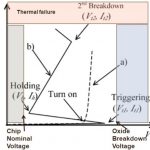

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center