You may already have heard today’s big news in the semiconductor fabless ecosystem that Intel is apparently in talks to buy Altera. I embarrassed myself predicting that Samsung were in talks to buy Freescale (which, of course, they might have been but NXP won that particular race). But this time it is definite enough that … Read More

Author: Paul McLellan

Full-chip Multi-domain ESD Verification

ESD stands for electro-static discharge and deals with the fact that chips have to survive in an electrically hostile environment: people, testers, assembly equipment, shipping tubes. All of these can carry electric charge that has the “potential” (ho-ho) to damage the chip irreversibly. Historically this was… Read More

25 Years of SNUG; 50 Years of Moore’s Law

Earlier this week it was the Synopsys user group meeting SNUG. Not just any old SNUG but the 25th Annual SNUG. The first one was 15th March 1991 and was attended by 100 people. At the time, Synopsys had annual revenues of $22M. This year, the various SNUGs around the world will have a total attendance of 10,000 people and Synopsys revenue… Read More

TSMC 2015 Technology Symposium

This year’s North American TSMC Technology Symposium is fast approaching. There are three, starting in Silicon Valley.

- San Jose on Tuesday April 7th at the San Jose Convention Center

- Boston on Tuesday April 14th at the Burlington Marriott

- Austin on Thursday April 16th at the downtown Hilton

The symposium will also take … Read More

A Brief History of Kilopass

Kilopass was founded back in 2001 by Jack Peng, whose background was in FPGAs with his most recent position being manager of technology development at Actel (now part of Microsemi). The idea was to build a company making one-time-programmable (OTP) memories using anti-fuse technology. Fuses in home-wiring (OK, I know, we all … Read More

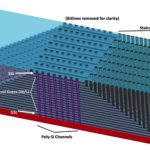

Vertical NAND Flash

You may know that up until now NAND flash has been a planar technology. But just as with SoC processes where we have had to go vertical to FinFETs, NAND flash has reached the limitations of scaling in the 20nm nodes and is also going vertical. It is not just a lithography issue but there are also reliability and voltage scaling issues.… Read More

SystemC Co-Simulation of NoCs and IP Blocks

Verification in general suffers from a couple of fundamental problems. Availability of models and performance of different levels of representation.

The first problem, availability of models, is that you would like to start verification as soon as possible but all the representations are not ready early enough. Obviously … Read More

SEMI: All This and Breakfast Too

Are you interested in any of these?

- Internet of Things

- Trends and Forecast for Fabs

- Inflections Points

- Semiconductor CAPEX

- Cost Effective Scaling

- Prospects for 450mm

- Future of EUV

- Mobile Machine Learning

- Robotics/Drones

- Cybersecurity

- Used Equipment Markets

- World Fab Databases

- Free breakfast

No? Then I think you got the wrong… Read More

Exploring IP You Didn’t Design Yourself

Starvision Pro from Concept Engineering is a bit like one of those Leatherman multi-tools, it has a huge number of different functions, some of them fairly specialized but nonetheless incredibly useful. Many of these functions are unique to Starvision Pro, with nothing else like it on the market. Some new videos, produced by EDA… Read More

FD-SOI Foundry

At the end of last month during ISSCC there was a forum organized by the SOI Consortium. It took place in San Francisco at the Palace Hotel (which, if you have never been there, is famous for converting its old entryway for carriages into an amazing dining room, and for a bar with a huge painting by Maxfield Parrish of the Pied Piper valued… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center