France exposure will be very strong at Las Vegas CES this year, the 3[SUP]rd[/SUP] country with 365 companies, behind USA and China. If you just take the start-up number into account, 274 French start-ups will be present, just behind the USA with 280 start-ups! If you look back, it’s a great jump compared with 2017 (178 start-up) … Read More

Author: Eric Esteve

French Tech at CES, 2nd country after USA with 274 Start-Up at Eureka Park!

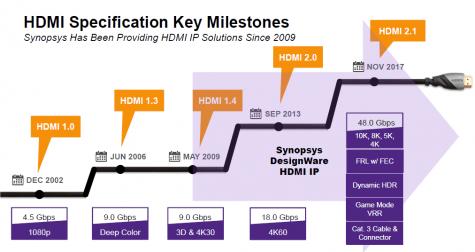

HDMI 2.1 Delivers 48.0 Gbps & Supports Dynamic HDR

You may or may not have bought HDMI-equipped device for black Friday or during year end break, but you TV set (or/and you PC) are certainly HDMI-powered, like the 750 million HDMI-equipped devices sold in 2016. In fact, cumulated shipment of HDMI-equipped devices has reached 6 BILLION since the protocol introduction in 2003! HDMI… Read More

Going to CES 2018? Don’t Miss CEVA-powered Demos!

CES 2018 will start soon and will be held on January 9-12 in Las Vegas. If you plan to go to Vegas, don’t miss CEVA-powered smart and connected products and demos! CEVA’s product portfolio includes DSP IP cores (the smart) and RivieraWaves IP platforms supporting wireless protocols, like WiFi and Bluetooth (the connected).

DSP … Read More

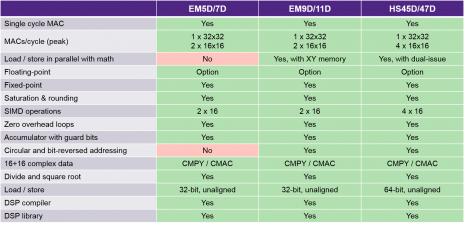

DSP Benchmarks and Libraries for ARC DSP families

Synopsys DesignWareARC HS4xD family is a perfect example of high performance DSP, enhanced RISC CPU IP core, able to address high-end IoT, mid to high-end audio or baseband control. ARC HS4xD architecture is 10-stage pipeline for high Fmax, resulting in excellent RISC efficiency with 5.2 CoreMark per MHz. ARC EMxD processors… Read More

IP-SoC 2017: IP Innovation, Foundries, Low Power and Security

The 20[SUP]th[/SUP] IP-SoC conference will be held in Grenoble, France, on December 6-7, 2017. IP-SoC is not just a marketing fest, it’s the unique IP centric conference, with presentations reflecting the complete IP ecosystem: IP suppliers, foundries, industry trends and applications, with a focus on automotive. It will … Read More

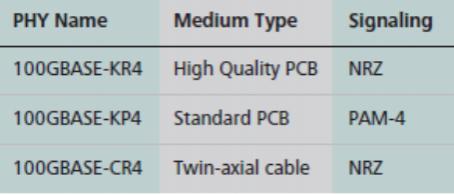

Multi-Channel Multi Rate FEC Engine Webinar with Open Silicon

I will be pleased to moderate on December 7[SUP]th[/SUP] the Open-Silicon webinar addressing the benefits of the multi-channel multi-rate forward error correction (MCMR FEC) IP and the role it plays in high-bandwidth networking applications, especially those where the bit error rate is very high, such as high speed SerDes … Read More

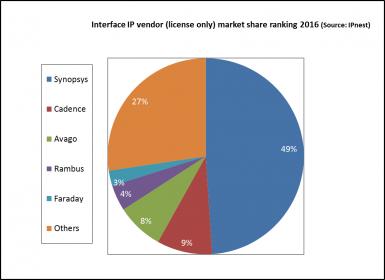

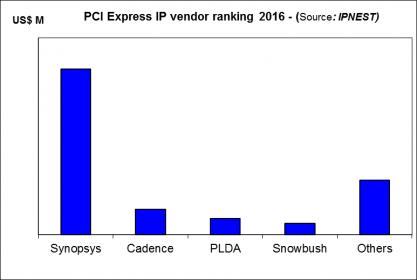

Worldwide Interface IP Revenue Grew by 13.5% in 2016 (Source: IPnest)

IPnest has released the 9[SUP]th[/SUP] version of the Interface IP Survey, ranking by protocol the IP vendors addressing the Interface segments: USB, PCI Express, (LP)DDRn, MIPI, Ethernet & SerDes, HDMI/DP and SATA. When the 1[SUP]st[/SUP] version has been issued in 2009, the IP segment was weighting $225 million and the… Read More

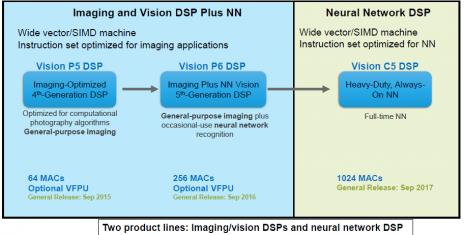

Tensilica Vision P6 DSP is Powering Huawei Kirin 970 Image

Cadence has recently announced two key design-in for their Vision DSP IP family: MediaTek’s Helio P30 integrates the Tensilica Vision P5 DSP and HiSilicon has selected the Cadence® Tensilica® Vision P6 DSP for its 10nm Kirin 970 mobile application processor. The Kirin 970 being integrated into Huawei’s new Mate 10 Series mobile… Read More

VESA DSC Encoder Enables MIPI DSI to Support 4K resolutions

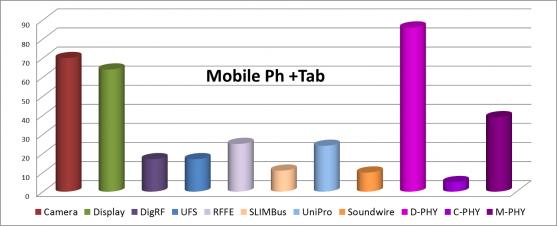

Some of the MIPI specifications are now massively used in mobile (smartphone), like the Multimedia related specs, Camera Serial Interface (CSI-2) and Display Serial Interface (DSI). These specifications are now adopted inautomotive infotainment systems, and augmented reality (AR)/ virtual reality (VR) devices. If you … Read More

The Interface IP Market has Grown to $530 Million!

According with IPnest, the Interface IP market, including USB, PCI Express, (LP)DDRn, HDMI, MIPI and Ethernet IP segments, has reached $532 million in 2016, growing from $472 million in 2015. This is an impressive 13% Year-over-Year growth rate, and 12% CAGR since 2012!

Who integrate functions to interface a chip with others … Read More

Solving the EDA tool fragmentation crisis