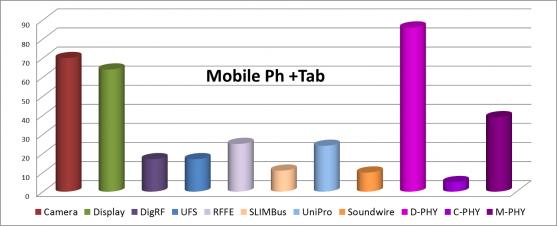

Some of the MIPI specifications are now massively used in mobile (smartphone), like the Multimedia related specs, Camera Serial Interface (CSI-2) and Display Serial Interface (DSI). These specifications are now adopted inautomotive infotainment systems, and augmented reality (AR)/ virtual reality (VR) devices. If you look at the picture below (MIPI Ecosystem survey 2015), MIPI DSI and the associated D-PHY are seeing a very high adoption level in mobile phone. We know that pervasion is strong beyond mobile: automotive or AR/VR.

But displays for these applications are becoming more sophisticated with quad HD or 4K resolutions at faster frame rates and support for RGB formats. This evolution has introduced new challenges for designers – managing the required data bandwidth while reducing power consumption and without compromising visual quality. Designers need a protocol that enables visually lossless compression over display interfaces like MIPI® Display Serial interface (DSI®).

The Video Electronics Standards Association (VESA) Display Stream Compression (DSC) standard offers visually lossless performance and low latency for ultra-high-definition (UHD) displays. VESA has collaborated with the MIPI Alliance to get the DSC standard adopted into the MIPI DSI standard. The challenge is to enable higher resolution, like 4K displays, which would require higher bandwidth, while keep using the mature, production proven MIPI D-PHY specification. MIPI DSI operates on the MIPI D-PHY physical link at 2.5 Gbps per four lanes yielding a maximum data rate of 10 Gbps per link. However, as outlined below, high-end video and image resolutions such as 4K and 3D 1080p require higher bandwidth:

– 4K: 24-bit RGB @ 60 frames per second (FPS) requires 13 Gbps (12 Gbps for active area)

– 3D 1080p: 24-bit RGB @ 60 FPS requires 12 Gbps (11 Gbps for active area)

For deeper color modes, bandwidth requirements are even higher, creating a problem that would normally require designers to increase DSI data lanes by re-architecting devices and redesigning circuits, which results in higher design time, cost and risk.

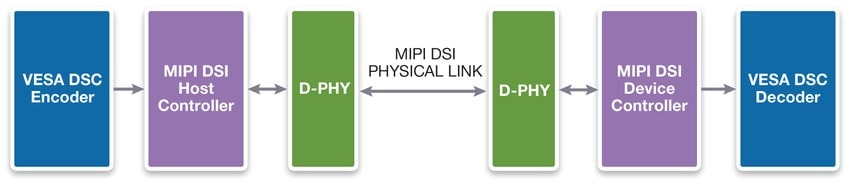

The solution came from VESA, defining Display Stream Compression (DSC) algorithm and the collaboration between MIPI and VESA has allowed incorporating DSC into DSI. According with VESA, DSI encapsulation into DSC protocol has provided “designers of source and display devices [with] a visually lossless, standardized way to transfer more pixel data over display links and to save memory size in embedded frame buffers in display driver ICs.” The Figure below shows a block diagram of VESA DSC integrated into MIPI DSI:

The VESA DSC algorithm can compress data in constant bit rate mode, providing a deterministic size stream that can be transported by DSI without further processing or padding. With VESA DSC, 4K and 3D 1080p video and image resolutions are now possible over existing display links.

– 4K, compressed to 12 bpp @ 60 FPS requires 6.5 Gbps –> 3 or 4 lanes- 4K, compressed to 8 bpp @ 60 FPS requires 4.4 Gbps –> 2, 3 or 4 lanes

– 3D 1080p, compressed to 12 bpp @ 60 FPS requires 6 Gbps –> 3 or 4 lanes

– 3D 1080p, compressed to 8 bpp @ 60 FPS requires 4 Gbps –> 2, 3 or 4 lanes

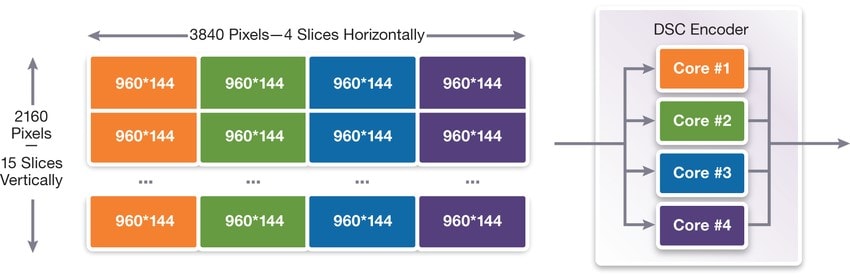

How to implement this compression? Before compression, an image is divided into a grid of slices. A DSC encoder, which can be made up of multiple cores that operate in parallel, applies compression to each slice independently. The next picture shows an example of how DSC cores can compress 4K image efficiently. The DSC encoder in this example (on the left) includes four cores and the image (on the left) is split into 4 columns by 15 rows, and each resulting slice is compressed by the corresponding DSC cores (indicated by color) in parallel.

Unlike compression standards such as H.264 or H.265, DSC does not use inter-frame compression, it offers very low latency and reduced memory size. DSC’s compression algorithm was designed to be implemented in hardware without the need for multimedia processors, making it highly efficient for area and power in SoCs.

Visually lossless compression is the ideal method to enable quad HD or 4K resolution embedded displays in high-end smart phones, automotive infotainment systems and AR/VR devices. The VESA DSC standard helps designers overcome bandwidth limitations associated with MIPI D-PHY without costly and risky circuit redesign. VESA DSC is an emerging standard that delivers visually lossless compression, providing designers flexible, low-latency, low-memory, and error-resilient results.

Synopsys has integrated VESA DSC into its silicon-proven DesignWare® MIPI DSI IP to enable quad HD or 4K resolution displays.

You can look at this articlefrom Synopsys, precisely describing how DSC and DSI can be implemented.

From Eric Esteve from IPnest

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.