… in 2019. At that time, the total Interface IP market is expected to weight between $900 million and $1 billion. If we want to understand this IP market segment dynamics, we have to look at protocol based products like USB (from USB 1.0 defined in 1996 at 12 Mbit/s to USB 3.1 supporting 10 Gbps data rate) or PCI Express (from PCIe gen-1… Read More

Author: Eric Esteve

Bye-Bye DDRn Protocol?

In fact, this assertion is provocative, as the DDR4 protocol standard has just been released by JEDEC… after 10 years discussion around the protocol features. Yes, the first discussions about DDR4 have started ten years ago! Will DDR4 be used in the industry? The answer is certainly yes, and DDR4 will most probably be used for years.… Read More

NVM Express Solution is Mainstream

Non Volatile Memory (NVM) is a superb technology, at least if you appreciate the physical law behind: storing a data in an embedded location with no physical link, as you charge a cell by influence and read it without physically accessing the stored data. Although the semiconductor industry is building NVM IC for about 30 years now,… Read More

The Technology to Continue Moore’s Law…

Can we agree about the fact that the Moore’s law is discontinuing after 28nm technology node? This does not mean that the development of new Silicon technology, like 14nm or beyond, or/and new Transistor architecture like FinFET will not happen. There will be a market demand for chips developed on such advanced technologies: mobile… Read More

DSP running 10 times faster at ultra-low voltage?

The LETI and STMicro have demonstrated a DSP that can hit 500 MHz while pulling just 460mV – that’s ten times better than anything the industry’s seen so far. Implemented on a 28nm FD-SOI technology, with ultra thin forward body biasing (UTFBB) capability (used to decrease Vth), this DSP can also be exercised at higher voltage when… Read More

Does Multiprotocol-PHY IP really boost TTM?

I have often written in Semiwiki about high speed PHY IP supporting Interface protocols (see for example this blog), the SoC cornerstone, almost as crucial as CPU, GPU or SDRAM Memory Controller. When you architect a SoC, you first select CPU(s) and/or GPU(s) to support the system basic functionality (Processor for Mobile application,… Read More

Yamaha Selecting Audio/Voice DSP Architecture?

…or Chongquing CYIT Communication Technology Co Ltd. Both of them have recently licensed the CEVA-TeakLite-4 DSP, the latest for its multi-mode wireless baseband chips targeting 4G terminals, including smartphones and tablets (CYIT) and Yamaha to address the need to run increasingly complex voice pre-processing algorithms,… Read More

$1 Billion IP & VIP sales by 2017?

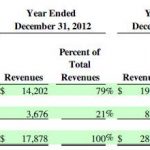

We are not talking about ARM Ltd., as the IP vendor has already passed the $1B sales in 2013. In fact, we are not talking about a single IP vendor; this $1B mark will be passed by two IP market segments: Interface and Verification IP. In fact these two segments are very close together. When an IP is developed to support a specific Interface… Read More

HDMI, DisplayPort, MHL IPs + Engineering Team = Good Move

This news is certainly not as amazing that the acquisition of MIPS by Imagination, or Arteris by Qualcomm… but it shows that Cadence is building a complete Interface IP port-folio, brick after brick. The result will be that a complete wall is being built on the Synopsys road to monopoly and complete success on Interface IP market.… Read More

If you still think that FDSOI is for low performance IC only…

…then you should read about this benchmark result showing how digital power varies with process corners, for high-speed data networking chip, not exactly the type of IC targeting mid-performance mobile application. Before discussing the benchmark results, we need to have some background about this kind of ASIC chip. Such a … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry