You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Last Monday I met with Nobuto Ono, VP Business development at Jedat (Japan EDA Technologies) while attending the DAC conference.

The company started in Tokyo and is Ex Seiko Instruments, in 2004.

Main product – layout editor for IC (SX 9000). New system is ALpha SX in 2002. 2007 listed on JASDAQ market. Like Virtuoso tools,… Read More

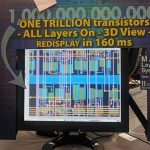

There are only a handful of billion transistor IC designs in existence today, so when an EDA company touts 1 trillion transistor IC layout editing then I take notice. This year at DAC I met with Katherine Hayes and Karen Mangum of Micro Magic to get an update on their IC layout tools.… Read More

I first heard about SPICE Vision Pro when working at Mentor Graphics where we needed a way to visualize SPICE netlists and debug SPICE simulation results node by node on a design where we didn’t have the original schematics. Last Monday I met the engineers from Concept Engineering in their booth at DAC to get an update, Gerhard… Read More

Monday at DAC I met with an EDA start-up called Symica based in Kiev. Ian Tsybulkin, CEO met with me to give an overview of their tools.… Read More

Linda Fosler, Tom Daspit and Mitch from Mentor Graphics met with me last Monday at DAC to provide an update on IC layout and circuit simulation tools. My notes follow:

Overview – Pyxis for Schematic and Layout, IC Station is re-branded as Pyxis. (Pyxis schematic is still Falcon, Ample language is still used.)… Read More

Cadence invited Francois Lemery of ST Microelectronics to speak at a luncheon last Monday at DAC about designing for the 20nm node using module generators. Here are my trip report notes:

… Read More

Before this DAC I had never even heard of ICScape, so on Monday and Wednesday I visited their booth to find out their story.

Steve Yang, Ph.D. (Co-founder and President), Ravi Ravikumar (Marketing)

ICScape was founded in 2005 in Santa Clara by Steve Yang (Circuit Design engineer for microprocessor, Synopsys) and Jason Xing (Sun… Read More

Britto Vincent of ProPlus Design Solutions met with me at DAC on Monday morning to talk about Design For Yield (DFY) and Analog Fast SPICE.

In 2011 ProPlus announced DFY tools where the technology came from IBM, it provides fast Monte Carlo results up to 3 sigma, then added NanoSpice for faster simulation results. Similar in approach… Read More

Wednesday morning I attended a panel discussion with: ARM, IBM, Cadence, GLOBALFOUNDRIES and Samsung.

The panelists all sang the same song of collaboration between EDA, IP and Foundry to enable 28nm, 20nm and even 14nm.… Read More

ARM and Synopsys are well-known physical IP companies however at DAC today I met with a lesser-known company named DXCORR that has some unique offerings for cache, multi-port memory and standard cell kicker libraries. I met with:… Read More

Solving the EDA tool fragmentation crisis