If your next SoC uses an ARM Cortex-A9 and has an industrial application, then you can save much design and debug time by using a prototyping platform. The price to prototype is quite affordable, and the methodology has a short learning curve. Bill Tomasan Aldec Research Engineer conducted a webinar today on: ARM Cortex SoC Prototyping… Read More

Author: Daniel Payne

Standard Cell Library Characterization

Standard cell library characterization has been around for decades, Synopsys has been offering Liberty NCXand Cadence has Virtuoso Foundation IP Characterization. What’s new is that Mentor Graphics acquired the Z Circuit technology for library characterization and has integrated it with the Eldo Classic circuit … Read More

Visually Debugging IC Designs for AMS and Mixed-Languages

With an HDL-based design methodology many IC engineers code in text languages like SystemVerilog and VHDL, so it’s only natural to use a text-based debug methodology. The expression that, “A picture is worth a thousand words” comes to my mind and in this case a visual debug approach is worth considering for … Read More

Image Sensor Design for IR at Senseeker

Image sensors are all around us with the cell phone being a popular example, and 35mm DSLR camera being another one. Last week I spoke with Kenton Veeder, an engineer at Senseeker that started his own image sensor IP and consulting services company. Instead of focusing on the consumer market, Kenton’s company does sensor … Read More

Learning Properties, Assertions and Covers for Hardware Design

How do you learn new hardware design topics? I just got trained online about property-based verification for hardware designers using a free online class at Aldec. The material was created by Jerry Kaczynski, a Research Engineer at Aldec.

FinFET Design Challenges at 14nm and 10nm

At DAC 2012 we were hearing about the 20nm design ecosystem viability, however IC process technology never stands still so we have early process development going on now at the 10nm and 14nm nodes where FinFET technology is being touted. Earlier in February Vassilios Gerousis, a distinguished engineer at Cadence presented a session… Read More

Modeling TSV, IBIS-AMI and SERDES with HSPICE

The HSPICE circuit simulator has been around for decades and is widely used by IC designers worldwide, so I watched the HSPICE SIG by video today and summarize what happened. Engineers from Micron, Altera and AMD presented on how they are using HSPICE to model TSVs, IBiS-AMI models and SERDES, respectively.… Read More

SPICE Circuit Simulation at STMicroelectronics

At the 2010 DACI moderated a panel session on SPICE and Fast SPICE circuit simulation, and one of the panelists was PierLuigi Dagliofrom STMicroelectronics. To get an update on SPICE circuit simulation at ST I read a PDF document at Mentor titled: Improving the Quality of SPICE Simulation Results with Eldo Premier at ST.

ST does … Read More

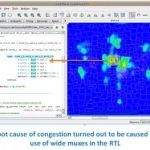

SoC Implementation, Sometimes You Need a Plan B

I read two blogs this week that got me to thinking about contingencies in SoC implementation. By contingency I mean using an EDA tool flow from the leading vendor for logic synthesis and then discovering that you cannot route the design without expanding the die size after a few weeks of concerted effort, then having to come up with… Read More

An Affordable AMS Tool Flow gets Integrated

EDA tools come in all sizes and price ranges, so I was pleased to readthat Tanner EDAhas completed an integration with Incentia. A few months ago Tanner announced their integration with Aldec for digital simulation, and today’s announcement extends their tool suite to include digital synthesis and static timing. Here’s… Read More

Solving the EDA tool fragmentation crisis