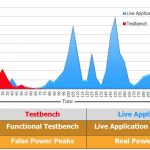

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

Author: Daniel Payne

Design Collaboration, Requirements and IP Management at #52DAC

For SoC designers attending DAC in June you probably want to check out the EDA vendors that enable design collaboration among your engineers and designers that are spread out across a building, campus or the globe. Dassault Systemes does offer tools and methodologies for: Design collaboration, requirements and IP management.… Read More

Saving Time and Money on Your Next SoC Project

Every SoC project that I know of wants to finish on time, under budget, and maximize profits per device. When I first started out doing DRAM design I learned that we could maximize profit by doing shrinks of existing designs, move from ceramic to plastic packages, and reduce the amount of time spent on a tester. Today, the economic … Read More

DAC, IP, Parties and Philanthropy

My typical DACtrip is a blur of non-stop interviews with EDA, IP and Semiconductor vendors followed by a few dozen blogs to share what I’ve learned. I just became aware of something a bit different at DAC this year by talking with Jill Jacobs, an organizer for an event dubbed Heart of Technology (HoT) where they raise money for… Read More

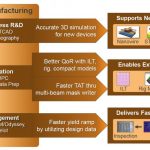

TCAD Enables Moore’s Law to Continue

We live in very interesting times, you can wear an Android watch from Samsung that uses 14 nm FinFET technology, attend the 52nd DAC conference in June to learn about EDA and IP vendors supporting FinFET, and read about research work for new devices down to 5 nm. TCAD is that critical software technology that enables the development… Read More

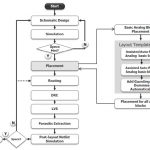

Can You Really Automate Analog IC Layout?

Digital IC design has been largely automated with high-level languages, RTL coding, logic synthesis, and automated place and route tools. What about analog IC layout automation, is it possible? A few EDA companies think that it is possible and even practical. In recent memory there were two companies really focused on analog … Read More

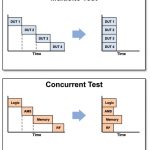

SoC Debugging Just Got a Speed Boost

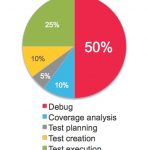

Sure, design engineers can get more attention than verification engineers, but the greater number of verification engineers on SoC projects means that the verification task is a bigger bottleneck in a schedule than pure design work. A recent survey conducted at Cadence shows how verification effort can be divided into several,… Read More

Networking at 52nd DAC in SFO

Yes, the 52nd DAC(Design Automation Conference) is a technical conference plus exhibition with wonderful keynote speakers and agenda, however there is a certain serendipity that occurs by just meeting people, face to face at the many networking opportunities. The best way to kick off your DAC experience is by attending the Sunday… Read More

Will your next SoC fail because of power noise integrity in IP blocks?

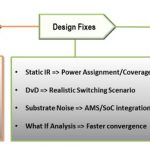

By the time that your SoC comes back from the fab and you plugin it into a socket on a board for testing, it’s a little late in the cycle to start thinking about reliability concerns like: dynamic voltage drop, noise coupling, EM (Electro-Migration), self-heating, thermal analysis and ESD (Electro-Static Discharge). They… Read More

What is Inside of the Samsung Galaxy S6?

I’ve always been curious about what is inside an electronic device, and it was seeing the very first TI handheld calculator that got me started into a career as an Electrical Engineer. Next to Apple, the most popular brand in smart phone devices these days has got to be Samsung and they have just launched the Galaxy S6 device.… Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem