Actual users of circuit simulators told their design and simulation stories at DAC during a luncheon sponsored by Synopsys on June 8th. I always prefer to hear from a design engineer versus a marketing person about what tool they use for circuit simulation, and how it helps them analyze their design goals. This year there were engineers… Read More

Author: Daniel Payne

Trends in Automotive Electronics at #52DAC

The coolest and most expensive car at DAC this year had to be the McLaren P1, priced at $1,150,00 and powered by a 903 hp gas/electric hybrid. Electronics are used in autos to provide safety features, infotainment, motor control and performance.

Also at DAC this year there was an Automotive Village with more cars and experts from … Read More

A Systems Company Update from #52DAC

On Sunday night at DAC we heard from Gary Smith that traditional EDA companies need to grow into new market segments in order to stay relevant, and that a systems-level approach to multi-disciplinary engineering was called for. I almost jumped out of my seat and said, “Hey, what about Dassault? They are already doing that … Read More

What’s New in Functional Verification Debug

We often think of EDA vendors competing with each other and using proprietary data formats to make it difficult for users to mix and match tools, or even create efficient flows of tools. At the recent DAC event in San Francisco I was pleasantly surprised to hear that two EDA vendors decided to cooperate instead of create incompatible… Read More

Predictions about EDA and IP at #52DAC

On Sunday night at DAC this week I sat in the front row and listened to Gary Smith give his predictions about EDA and IP as an industry. His financial forecast was a $6.8B industry in 2015, growing to $9B in 2019. An ideal company for Wall Street to invest in would have slow and steady growth. If you add semiconductor IP into the forecast… Read More

Turning the Automotive Development Process Upside Down

Most of us drive automobiles and have a vague idea that the development of our cars takes many years, millions of dollars, is a proprietary process and require huge factories to produce. A relatively new company called Local Motors founded in 2007 has started to turn the automotive development process upside down because they do… Read More

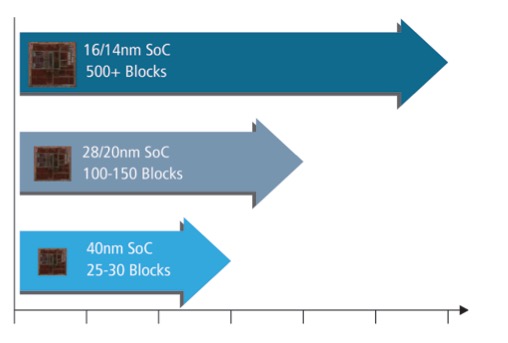

Logic Synthesis Reborn

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

Even More Integration and Automation for ARM-based Designs

The attraction to an IP-based design methodology is that you can assemble an SoC from ready-made IP blocks, saving you valuable engineering development and verification time, while reducing risks from having to develop something from scratch and hoping that they meet industry standard specs. ARM is well known for supplying … Read More

The State of Desktops, Notebooks and Tablets

The personal computing market started out back in the late 1970’s, with IBM being a relative late-comer in 1981, however over many decades we’ve seen the unit volumes steadily increasing each year driving demand of semiconductors of all types. IC Insights is a research company that follows the personal computer … Read More

NVIDIA and Qualcomm Talk about High Level Synthesis, Samsung on Low Power for Mobile

Since 1978 I’ve seen many trends in the semiconductor design world: transistor-level IC design, gate-level design, RTL coding, High Level Synthesis (HLS) and IP re-use. We’ve witnessed the growth in design productivity enabling chips starting with just thousands of transistor all the way up to billions of transistors… Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem