EDA vendors have long used proprietary file and database formats to keep their users locked into their specific tool flow and keep any competitors from sharing in the IC design process. Along the way the actual users of EDA tools have often requested and helped to create interoperable flows so that they could mix and match multiple… Read More

Author: Daniel Payne

The Age of Automotive Electronics

One of Intel’s most advanced fabrication sites is called Ronler Acres, located in Hillsboro, Oregon and I jumped at the opportunity to visit this site on April 26th when members from the SEMI Pacific Northwest Chapter are meeting to discuss a timely topic, “The Age of Automotive Electronics”. The previous … Read More

Sustainability, Semiconductor Companies and Software Companies

I certainly want to leave the Earth a better place to live for my children and generations to come, so sustainability is a value that resonates with me. How is a consumer like me to know which companies are the most sustainable in areas that matter, like:… Read More

Smart Phones and the Chinese Marketplace

My first mobile phone was from Motorola and it was fondly called the “brick phone” because of its crude shape. That phone helped me be more efficient while living and working in Silicon Valley, because long commute times in the car were common. At one time Motorola was the best-selling mobile phone brand in the world,… Read More

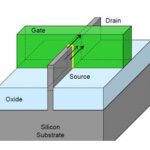

How 16nm and 14nm FinFETs Require New SPICE Simulators

About 35 years ago the first commercial SPICE circuit simulators emerged and they were quickly put to work helping circuit designers predict the timing and power of 6um NMOS designs. Then we had to limit our circuit simulations to just hundreds of transistors and interconnect elements to fit into the RAM and complete simulation… Read More

The Mechanical Reliability of IC Packages

At Intel back in the late 1970’s we were designing DRAM chips and mounting them in ceramic and plastic packages, however there were problems when some of the die would crack inside of the package because of thermal mismatch issues with how the die was attached to the heat spreader inside the package. Back then we really didn’t… Read More

Semiconductor IP Comes of Age

I love reading about good news in the EDA and Semiconductor IP space, especially in light of the recent stock market trending downward in January. The best news that I’ve read in the past week is about the Q3 2015 revenue numbers collected by EDAC, because it shows that Semiconductor IP (SIP) surpassed CAE tool revenues for … Read More

Cycling Product Update from CES 2016

Cycling is part of the overall fitness industry which is enjoying a surge of new semiconductor-enabled devices to help us measure our progress, so at CES 2016 there’s plenty of activity on this front. I’ll highlight some of the more notable new product developments from the show.… Read More

Inventor of Netscape Looks at IoT

1995 was the year that a co-worker walked into my cubicle and said, “Hey, you have to see this new web browser and Internet thing.” I promptly installed Mosaic, later renamed Netscape, and began surfing the web with all of those interesting hyperlinks bringing me to new articles. Marc Andreessen was the mastermind … Read More

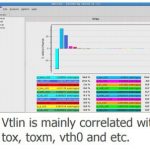

Tuning Analog IP for High Yield at SMIC

Analog IP is more difficult to design and optimize for a given process node compared to digital IP, so any automation for analog designers is always welcome. The engineers at SMIC in China have customers that design analog IP and often they need to know how to optimize it for a specific process, so I watched a presentation by Josh Yang,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?