Kevin Ashton, a British technology pioneer, is credited for the term “The Internet of Things” to describe an ecosystem where the Internet is connected to the physical world via ubiquitous sensors. Simply stated: rather than humans creating content for the internet IoT devices create the content. To be clear, this… Read More

Author: Daniel Nenni

Fabless: The Transformation of the Semiconductor Industry

As I have mentioned before, Paul McLellan and I are writing a book on the history of the fabless semiconductor industry. There is a preview available HERE, it will initially be sold as an e-book on SemiWiki and put into print early next year. Working with Paul McLellan and Beth Martin on this was an amazing experience. The research,… Read More

Webinar: IP Lifecycle Management: What is it, what problems does it solve?

SoC’s are now dominated by IP blocks sourced either from 3rd parties or internal design teams. This means that IP is now critical to the success of the SoC, yet it is part of the design that teams have the least control over, or visibility into. Most design teams utilize at best ad-hoc methods to manage this IP, and the few that utilize… Read More

Intel is Killing the Environment!

If I had to sum up opening day at ARM TechCon 2013 in one word it would be “crowded”. More than twice as many people attended as last year with 6,500 preregistered. The opening keynote was “The New Style of IT” pimping the HP Moonshot systems, but it could have just as easily been called “Why Intel Stock is Dead Money”,… Read More

TSMC ♥ Mentor (Calibre PERC)

As semiconductors become more integrated into our lives reliability is becoming a critical issue. As IP consumes more of our die, IP reliability is becoming a critical issue. As we pack more transistors into a chip, reliability is becoming a critical issue. As we move from 28nm to 20nm to 16nm, reliability is becoming a critical … Read More

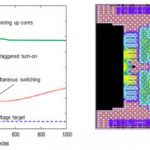

Strategic Analog IP Power Management for SoCs

This tutorial describes how analog IP is becoming more important in any power management strategy and shows the major analog building blocks to manage power and temperature in a SoC on leading edge technology nodes.

The tremendous demand for high-performance computing devices has led to aggressive technology scaling, allowing… Read More

An Affair to Remember: EDA’s 50th Anniversary

What an amazing night! I celebrated the 50[SUP]th[/SUP] anniversary of the industry I grew up in! With my beautiful wife at my side and a table full of friends we all went down memory lane, ate, drank, and then enjoyed the auction.

The tour of the new computer museum was amazing. I was learning so much up until the 1970’s, then … Read More

TSMC ♥ Synopsys (HSPICE)

In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

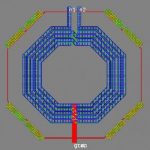

EM Solver and Visualization Essential for Device Design

In many designs, an on chip inductor is created as though it were simply a device with an L and a Q value. Of course this view would seem to make life simpler for designers and the tools they use. But in reality even a simple inductor is really a complex compound structure with many electromagnetic elements interacting in complex ways.… Read More

Analog & Mixed-Signal Design Lunch & Learn

I’m a big fan of lunch and learns, mainly because I’m a big fan of lunch but I also like to learn. I’m also a big fan of Tanner EDA which is why I helped organize this event. Face to face interaction amongst the fabless semiconductor ecosystem is critical to our success so stop on by and network, lunch is on me.

Take a look at the Brief History… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior