If you have a phone, you probably know it has a SIM card, for most of us the anchor that ties us into a 2/3-year plan with one network provider, unless you have an unlocked phone. Even then, you have to mess around swapping SIM cards if you travel overseas. Wouldn’t it be nice if the SIM was embedded and could be switched though an app or an… Read More

Author: Bernard Murphy

Webinar: Bottlenecks be Gone – Automated Performance Verification with Synopsys

Performance verification is among the most challenging of objectives in any SoC verification plan. It’s difficult to start effectively until quite late in the development cycle, at which point you don’t have a lot of time left to develop extensive performance-oriented testbenches. So many teams adapt functional tests to this… Read More

More Than Your Average IP Development Kit

When I think of an IP development kit, I imagine software plus a hardware model I can run on a prototyper or, closer to the kits offered by semi companies, software plus a board hosting an FPGA implementation of the IP along with DDR memory, flash and a variety of interfaces. These approaches work well for IP providers because hardware… Read More

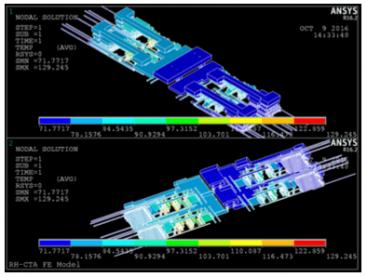

Webinar: Multiphysics Reliability Signoff for Next-Generation Automotive Electronics Systems

In case you missed the TSMC event, ANSYS and TSMC are going to reprise a very important topic – signing-off reliability for ADAS and semi-autonomous /autonomous systems. This topic hasn’t had a lot of media attention amid the glamor and glitz of what might be possible in driverless cars. But it now seems like the cold light of real … Read More

CES: An Exhibitor’s Takeaway

There are few tech promises these days as prominent as those surrounding driverless cars (trucks, buses, …). But thanks to always-on media amplifiers, it’s not always easy to separate potential from reality. I recently talked to Kurt Shuler, VP Marketing at Arteris, who shared his view after returning from this year’s CES. Kurt… Read More

Crystal Bulb: Sharing Design Intelligence

There is a trend among design companies to want to extract more intelligence, from designs in-process and designs past, in support of optimizing total enterprise efficiency. Design automation companies see opportunity in leveraging this interest since they, in various ways, have a handle on at least part of the underlying data.… Read More

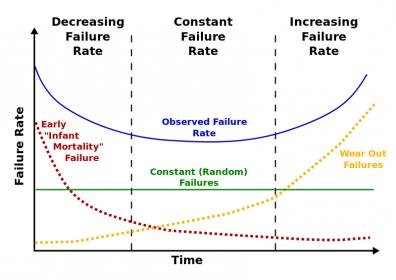

Conflating ISO 26262 and DO-254

If you’re in the ASIC business, by now you should have a rough understanding of ISO 26262, the safety standard for automotive electronics. You may be less familiar with DO-254 which has somewhat similar intent for airborne electronics. Unless, that is, you design with FPGAs in which case your familiarity may be the other way around… Read More

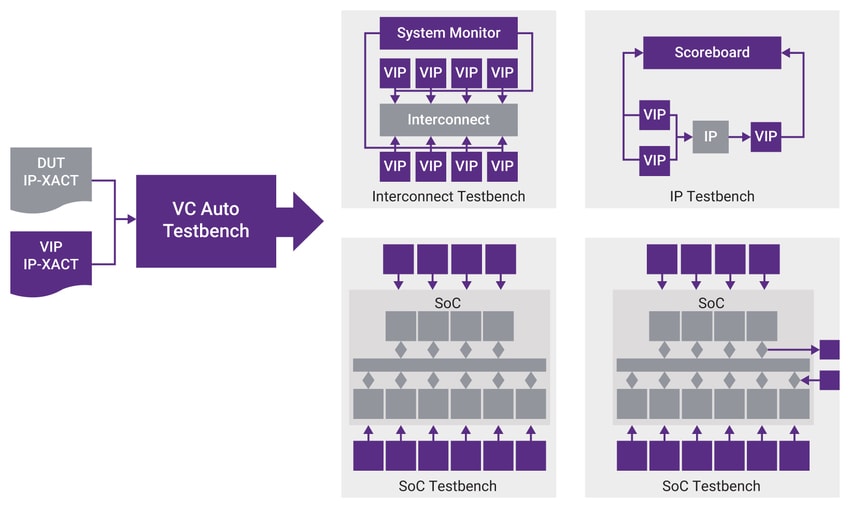

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

Simulation and Formal – Finding the Right Balance

Simulation dominates hardware functional verification today and likely will continue to dominate for the foreseeable future. Meanwhile formal verification, once thought to be a possible challenger for the title, has instead converged on a more effective role as a complement to simulation. Formal excels at finding problems… Read More

Thermal Modeling for ADAS goes MultiPhysics

In electronic system design, we have grown comfortable with the idea that different regimes of analysis, such as the chip, the package and the system, or electrical, thermal and stress are more or less independent – what starts in one regime stays in that regime, give or take some margin information passed onto other regimes. And… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!