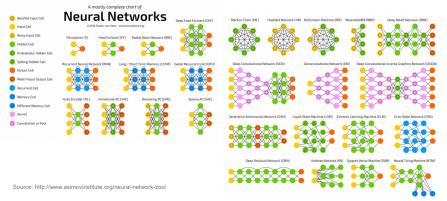

Machine learning (ML), and neural nets (NNs) as a subset of ML, are blossoming in all sorts of applications, not just in the cloud but now even more at the edge. We can now find them in our phones, in our cars, even in IoT applications. We have all seen applications for intelligent vision (e.g. pedestrian detection) and voice recognition… Read More

Author: Bernard Murphy

Another Application of Automated RTL Editing

DeFacto and their STAR technology are already quite well known among those who want to procedurally apply edits to system-level RTL. I’m not talking here about the kind of edits you would make with your standard edit tools. Rather these are the more convoluted sort of changes you might attempt with Perl (or perhaps Python these days).… Read More

An Advanced-User View of Applied Formal

Thanks to my growing involvement in formal (at least in writing about it), I was happy to accept an invite to this year’s Oski DVCon dinner / Formal Leadership Summit. In addition to Oski folks and Brian Bailey (an esteemed colleague at another blog site, to steal a Frank Schirrmeister line), a lively group of formal users attended… Read More

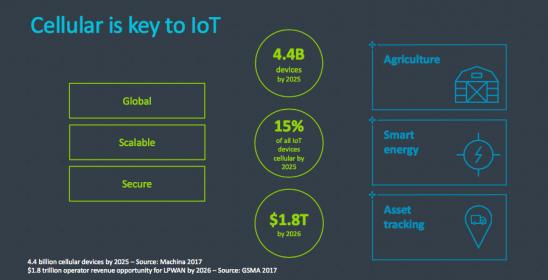

ARM and embedded SIM

It seems that a hot ticket at Mobile World Congress this year was embedded SIM announcements. As a reminder of why this space is hot, cellular communication for provisioning and data uploads is a very real option for many IoT devices. In agricultural, smart energy and asset tracking applications for example, near-range options… Read More

Concluding Inconclusives

Formal methods are a vital complement to other tools in the verification arsenal, but they’re not without challenges. One of the more daunting is the “inconclusive” result – that case where the tool seems to be telling you that it simply gave up trying to figure out if a particular assertion is true or false. Compounding the problem,… Read More

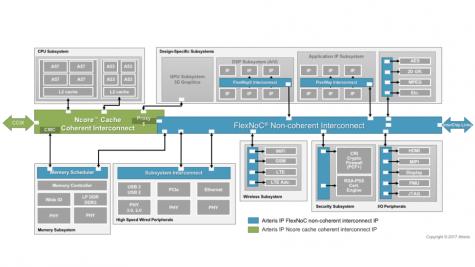

Connecting Coherence

If a CPU or CPU cluster in an SoC is the brain of an SoC, then the interconnect is the rest of the central nervous system, connecting all the other processing and IO functions to that brain. This interconnect must enable these functions to communicate with the brain, with multiple types of memory, and with each other as quickly and predictably… Read More

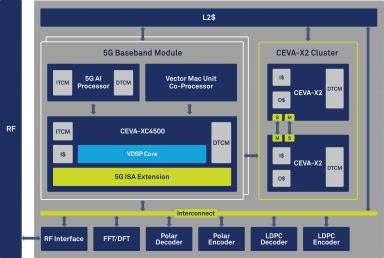

An AI assist for 5G enhanced Mobile Broadband for mobile platforms

If you’re not up-to-speed on 5G, there are three use-cases: eMBB(enhanced mobile broadband) for mobile platforms (Gbps rates, immersive gaming, VR, AR – spectrum usage also extends up to mmWave, but that’s a different topic), mMTCfor massive machine type communication (ultra-low cost, ultra-low power, very dense networks)… Read More

A Development Lifecycle Approach to Security Verification

We have become accustomed to the idea that safety expectations can’t be narrowed down to one thing you do in design. They pervade all aspects of design from overall process through analysis, redundancies in design, fault analytics and mitigation for faults and on-board monitors for reliability among other requirements and techniques.… Read More

Securing embedded SIMs

If you have a phone, you probably know it has a SIM card, for most of us the anchor that ties us into a 2/3-year plan with one network provider, unless you have an unlocked phone. Even then, you have to mess around swapping SIM cards if you travel overseas. Wouldn’t it be nice if the SIM was embedded and could be switched though an app or an… Read More

Webinar: Bottlenecks be Gone – Automated Performance Verification with Synopsys

Performance verification is among the most challenging of objectives in any SoC verification plan. It’s difficult to start effectively until quite late in the development cycle, at which point you don’t have a lot of time left to develop extensive performance-oriented testbenches. So many teams adapt functional tests to this… Read More

Is Intel About to Take Flight?