I am a fan of product releases which bundle together multiple high-value advances. That approach reduces the frequency of releases (no bad thing) in exchange for more to offer per release, better proven through solid partner validation. The Dynamic Duo III release falls in this class, offering improvements in performance, capacity, and solution support across this matched set of hardware-assisted verification engines (Palladium for emulation and Protium for prototyping).

Capacity and performance advances

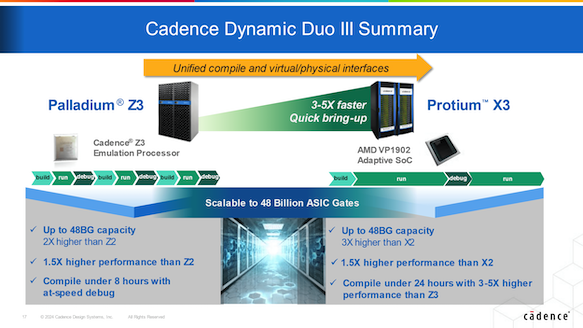

It’s a very worn marketing cliché but still true that design sizes keep growing hence the tools to support verification must continue to grow with them. The new generation Palladium Z3 and Protium X3 systems have increased total supported capacity, to 48 billion usable gates and each offer a 50% boost in performance. The Palladium platform is based on a new generation of the Cadence custom emulation processor and the Protium platform is based on the recently released AMD VP1902 device.

Compile times have improved dramatically on large designs through a new modular compiler, delivering near constant compile times independent of design size. For Palladium this maxes out at 8 hours per compile, making 1-2 verification turns per day a reality in early-stage system verification runs. Protium compile times have also dropped, to under 24 hours, speeding prototyping turns in late-stage hardware/firmware validation. Naturally the signature tight coupling between platforms continues with Z3 and X3, allowing for example a run exhibiting a bug in X3 prototyping to be flipped over to Z3 emulation for detailed debug drill-down.

Both platforms continue to deliver form factor and power optimization suitable to enterprise resources, allowing for maximum utilization whether verifying IP, subsystem/chiplet, or full system scale while packing as many jobs as will fit into available resource given job sizes. Both are also available as cloud-based resources.

Since Nvidia has been a long-time fan, I have to believe hardware development for LLMs is among leading drivers motivating these improvements.

Solution apps

Bigger and faster are always important but what really caught my attention in this release are the apps. First, Cadence have spun a new power estimation/analysis app (DPA 3.0), claiming 95% accuracy compared to implementation-level static power analysis (the pre-silicon power signoff of record). Not a new capability of course but sounds like it is much improved and of course running on a platform which can run very big designs with serious use-cases, always important when teasing out power bugs in big systems.

The 4-state emulation app is particularly interesting. Samsung presented a paper at DVCon this year on how they use this capability (currently unique to Palladium apparently) for low power debug. As an example, when switching power states, there are numerous opportunities for bugs to arise around incorrectly enabled isolation logic. X-propagation tests are a good way to catch such bugs but classic X-prop verification using simulation or formal is limited to relatively small design and test sizes. Emulation has the necessary capacity and speed but has historically only supported 0/1 modeling. Now Palladium Z3 also supports 0/1/X/Z as an option, making X-prop testing a very real option on big designs and tests. Samsung were able to show 100X performance improvement in this analysis over a simulation-based equivalent.

In mixed signal emulation, ADI presented an award-winning poster at the same DVCon on their use of the new Palladium app for digital mixed signal (DMS). I believe DMS emulation will become a must-have for 5G, 6G and beyond, to verify correctness between RF and digital stages as software-dependent coupling between stages increases. ADI say their testing shows the methodology is ready for production use, with some limitations and workarounds. Not surprising when forging a new frontier.

The Palladium safety app brings fault simulation to emulation – now we can talk about fault emulation 😀. Michael Young (Sr. Product Management Group Director, Cadence) tells me that speedup versus heavily parallelized software-based fault sim is typically 10-100X. He adds that a common use model is to do most of the relatively short sims using the software platform and to port longer analyses (1 hour or more) to the emulator. The Xcelium safety app and the Palladium share the same fault campaign model so switching between platforms should be simple.

Good fundamentals and good new features in this release. You can read more HERE.

Also Read:

Fault Simulation for AI Safety. Innovation in Verification

Challenge and Response Automotive Keynote at DVCon

Automotive Electronics Trends are Shaping System Design Constraints

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.