As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges as well to handle power distribution, tackle inter-die thermal issues and maintain signal integrity. Other than that 3D-ICs bring a typical issue of accommodating heterogeneous dies with designs at different technology nodes. As technologies and designs have progressed to newer ventures, EDA tools have always kept pace with them to provide best automation in getting volume production.

Today, ANSYS has a great suite of tools which can very accurately analyze power, noise and reliability for any chip taking into account its package and system level interactions as well. These tools are capable of handling all kinds of issues including inter-die effects that arise in 3D-ICs.

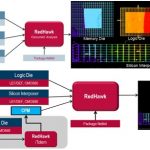

RedHawk can perform multi-die (each die can have design at different process node) power integrity analysis with or without shared power/ground nets. It can do concurrent analysis when detailed data for each die is available; in case physical data is not available for any particular dies then also it allows early design analysis by using power models (CPM) for those dies.

In 3D-IC, there is a tendency of heat getting trapped between dies which can lead to electro migration (EM) effect and that can cause opens and shorts getting build up in the design. The allowable current density of wires also gets affected. The thermal analysis using Chip Thermal Model (CTM), package model, and system level heat transfer coefficients enables generation of temperature profiles on 3D-IC components including chip metal layers, package, and bump/micro-bump/TSV for accurate thermal-aware EM methodology. Also, with higher current densities, the ESD analysis across dies must be performed.

ANSYS offers solution with proven tools to model wide-IO jitter for an interposer or 3D-IC design, extract channel parasitic and analyze the impact of SSN channel design on power and signal integrity of the design. Parasitic of a single TSV in a uniform array or hundreds of TSVs in an irregular array can be accurately extracted. The package and die can be taken into consideration to co-optimize decap as well.

ANSYS provides excellent modeling capabilities that are Spice-accurate and take into account the operating conditions, parasitic and temperature effects. CPM (Chip Power Model) is a compact model for full-chip power delivery network that contains switching current profile as well as parasitics of on-chip non-linear devices including decaps, loading capacitance and power/ground coupling capacitance. It accurately models the electrical response of the chip for a wide range of frequency, from DC to multi-GHz, thus enabling the analysis and optimization of system-level power integrity designs.

Generated by RedHawk and Totem, CTM (Chip Thermal Model) is a comprehensive chip-level thermal model based on chip’s operating conditions, its layout and specialized temperature-dependent power libraries. It captures the power and current inside a chip as a function of temperature, location, electrical activity, interconnect, layer-by-layer metal density and thermal conductivity of materials on silicon and package for accurate simulation. Sentinel-TI uses CTM to perform accurate closed-loop chip-package-system thermal analysis.

Similarly, CSM (Chip Signal Model) is used for SSO (Simultaneous Switching Output) simulation; it takes into account the power and ground rails on the die and hence the output characterization is power/ground noise dependent. TSVs (Through Silicon Via) have to be extracted with all parametric values and modeled for accurate power/signal integrity and reliability analyses. ANSYS provides capability to extract 1000s of TSVs in a large array and create accurate 3D EM models to capture frequency dependency and crosstalk. Sentinel-TI can be used to generate comprehensive finite element simulation models for chip package that can be used to simulate the effects of thermal and mechanical stresses on the chip package.

Look for more details on ANSYS solution and offerings from other EDA vendors as well as designers and manufacturers for 3D-IC design solutions in the upcoming 3D ASIP conference to be held on Dec 10 – 12, 2014 in Burlingame, CA.

Norman Chang, VP Design Solutions at ANSYS will be presenting in Preconference Symposium as well as in a special session dedicated to “Design Analysis and Modeling – Signal Integrity, Thermal and Power Considerations”. Attend these presentations as per the schedule below –

Preconference Symposium

Dec 10, 2014, 8:30AM – 12:30PM – 2.5/3D-IC Design Tools and Flows

Session 5: Design Analysis and Modeling – Signal Integrity, Thermal and Power Considerations

Dec 11, 2014, 3:30PM – 5:30PM – Performing 3D-IC Design Trade-off with Fast Power/Thermal/Signal Integrity Analyses for Early Design Stages