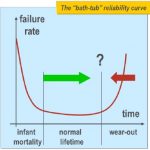

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to sustain through their lifetimes. Automotive devices typically have longer lifetimes which can last for ten or more years. There can be several factors that can degrade the reliability of a device, thus affecting its lifetime. The major reliability degradation factors include NBTI (Negative Bias Thermal Instability), HCI (Host Carrier Injection), and TDDB (Time Dependent Dielectric Breakdown). How to predict the life of an IC amidst such degradation effects?

The effects such as BTI and HCI have to be modeled and simulated. For analog and RF circuits, advanced analog and mixed-signal simulators are used which need to simulate the circuit efficiently and provide accurate results including statistical aging analysis. The reliability and aging analysis must be done early in the design cycle to avoid product recall later which may incur significant loss to the company.

Mentor Graphicshas a very effective and efficient verification flow for reliability which uses their Eldo circuit simulator. It compares the behavior of a fresh circuit just out of fab against the behavior of the same circuit aged after N years of operation under arbitrary periodic conditions. The lifetime of the fresh circuit can be predicted from the comparison of results.

Eldo uses a model which computes instantaneous stress of transistors subject to a given bias and temperature. The stress for each device is computed and integrated during normal simulation. The accumulated stress after Y years is computed by linear extrapolation. Eldo uses another set of equations which model the way ‘fresh’ model parameters are modified into ‘aged’ ones by this accumulated stress. A new ‘aged’ simulation is run using these updated model parameters. This flow can be performed, either quickly in 2 steps or in N steps. The N-step flow can provide more accurate results, however it will be slower by N times.

The aging by nature is a statistical process. Two identical devices can have slightly different threshold voltages, drive currents, and leakage currents. They also can have different aging profiles. Even if the bias conditions are identical, they do not age the same way. The required measurements are complicated, lengthy and costly. Eldo UDRM (User Defined Reliability Model) extensions support Monte Carlo simulation on aging parameters; supported models include BSIM3/4SOI, PSP, HiSIM etc.

The aging sensitivity analysis provides insight about which aging device is important and has most impact on outputs. A significantly degraded device may have little impact on circuit performance whereas a little degraded device may have significant impact on output performance. The reliability analysis with Harmonic Balance Steady-State is supported for RF circuits.

Eldo UDRM flow provides a robust and flexible solution for reliability analysis of ICs. It supports customizable aging models in Spice and Verilog-A languages. The reliability simulation offers encryption mechanisms to protect intellectual property of equations and models of degradation effects. The advanced model definitions allow designers to account for these degradation effects much early in the design.

This methodology was presented in 52[SUP]nd[/SUP] DAC at Mentor booth by Ahmed Eisawy, Eldo Product Marketing Manager at Mentor. Also, there is a case study done by Vitessewhich is posted on Mentor website; Joint Design – Reliability flows and advanced models address IC reliability issues. This case study also shows how reliability issues can be debugged by visualizing instantaneous stress pulses as experienced by the device.

Pawan Kumar Fangaria

Founder & President at www.fangarias.com